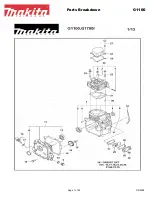

6.18 Typical Characteristics: Current Output (continued)

at T

A

= 25°C, V

DD

= 5.5 V, output range: ±250 μA (unless otherwise noted)

Code

Curr

en

t Output

DNL (LSB

)

0

32

64

96

128

160

192

224

255

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Channel 1

Channel 0

Output range: 0 μA to 250 μA

Figure 6-36. Current Output DNL vs Digital Input Code

Code

Curr

en

t Output

DNL (LSB

)

0

32

64

96

128

160

192

224

255

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Channel 1

Channel 0

Output range: 0 μA to –240 μA

Figure 6-37. Current Output DNL vs Digital Input Code

Temperature (

C)

Curr

en

t Output

DNL (LSB

)

-40

-25

-10

5

20

35

50

65

80

95

110 125

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

CH1 MAX

CH0 MAX

CH1 MIN

CH0 MIN

Figure 6-38. Current Output DNL vs Temperature

Supply Voltage (V)

Curr

en

t Output

DNL (LSB

)

1.8

2.725

3.65

4.575

5.5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

CH1 MAX

CH0 MAX

CH1 MIN

CH0 MIN

Figure 6-39. Current Output DNL vs Supply Voltage

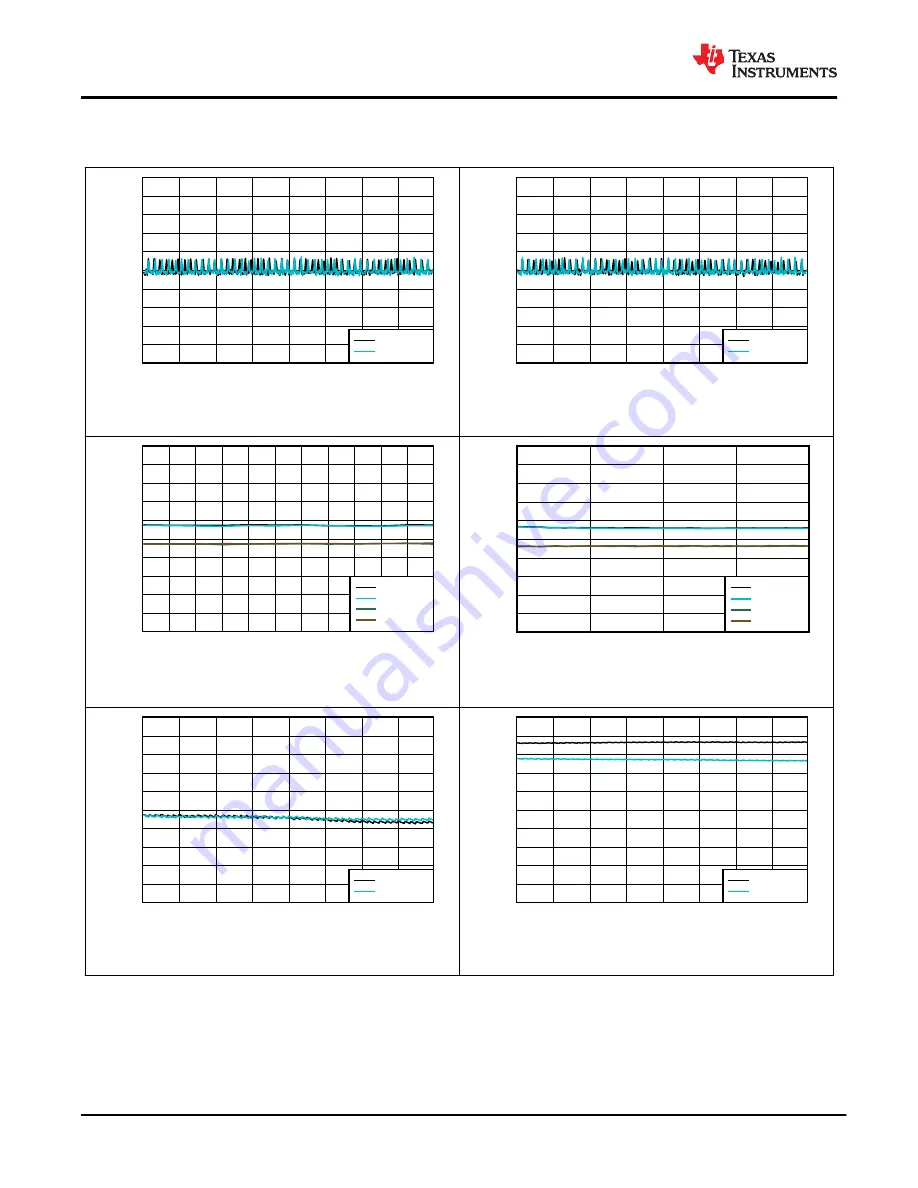

Code

Curr

en

t Output

TUE (%F

S

R)

0

32

64

96

128

160

192

224

255

-2

-1.6

-1.2

-0.8

-0.4

0

0.4

0.8

1.2

1.6

2

Channel 1

Channel 0

Figure 6-40. Current Output TUE vs Digital Input Code

Code

Curr

en

t Output

TUE (%F

S

R)

0

32

64

96

128

160

192

224

255

-8

-6.4

-4.8

-3.2

-1.6

0

1.6

3.2

4.8

6.4

8

Channel 1

Channel 0

Output range: 0 μA to 250 μA

Figure 6-41. Current Output TUE vs Digital Input Code

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

20

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: