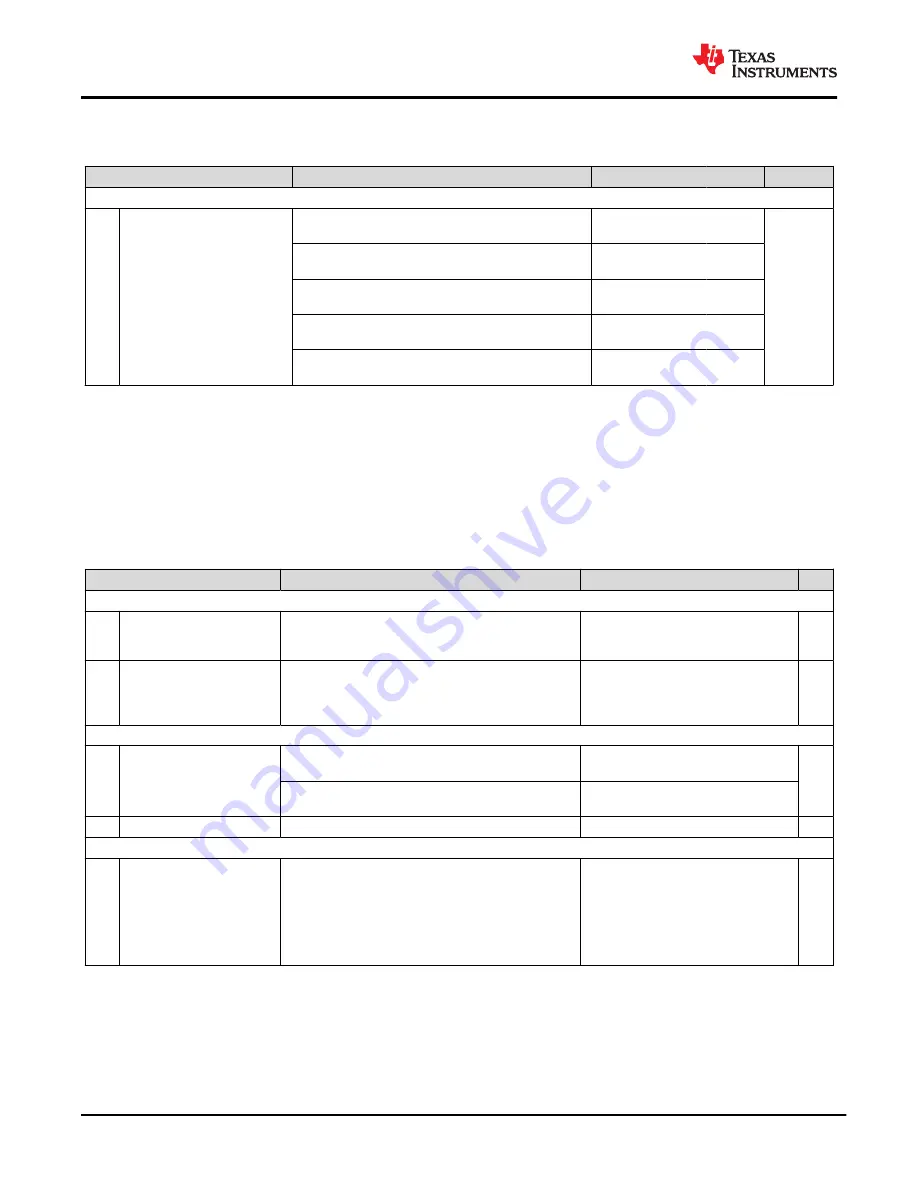

6.6 Electrical Characteristics: Current Output (continued)

at 1.7 V ≤ V

DD

≤ 5.5 V, ±250-µA output range, digital inputs at VDD or AGND, all minimum and maximum specifications at

–40°C ≤ T

A

≤ +125°C, and typical specifications at T

A

= 25°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

POWER

I

DD

Current flowing into VDD

Normal operation, DACs at midscale, all unipolar

output ranges, digital pins static

18

24

µA/ch

Normal operation, DACs at full scale, ±25-µA output

range, digital pins static

42

50

Normal operation, DACs at full scale, ±50-µA output

range, digital pins static

56

70

Normal operation, DACs at full scale, ±125-µA output

range, digital pins static

98

120

Normal operation, DACs at full scale, ±250-µA output

range, digital pins static

167

200

(1)

Measured between DAC codes 0d and 255d.

(2)

Specified by design and characterization, not production tested.

(3)

The current flowing into V

DD

does not account for the load current sourced or sinked on the OUTx pins. The VREF pin is connected to

V

DD

.

(4)

The total power consumption is calculated by I

DD

x (total number of channels powered on) + (sleep-mode current).

6.7 Electrical Characteristics: Comparator Mode

at 1.7 V ≤ V

DD

≤ 5.5 V, DAC reference tied to VDD, gain = 1x in voltage output mode, DAC output pin (OUT) loaded with

resistive load (R

L

= 5 kΩ to AGND) and capacitive load (C

L

= 200 pF to AGND), digital inputs at VDD or AGND, all minimum

and maximum specifications at –40°C ≤ T

A

≤ +125°C, and typical specifications at T

A

= 25°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

STATIC PERFORMANCE

1.7 V ≤ V

DD

≤ 5.5 V, DAC at midscale, comparator

input at Hi-Z, and DAC operating with external

reference

–5

0

5 mV

Offset error time drift

V

DD

= 5.5 V, external reference, T

A

= 125°C, FBx in

Hi-Z mode, DAC at full scale and V

FB

at 0 V or DAC

at zero scale and V

FB

at 1.84 V, drift specified for 10

years of continuous operation

4

mV

OUTPUT

Input voltage

VREF connected to VDD, FBx resistor network

connected to ground

0

V

DD

V

VREF connected to VDD, FBx resistor network

disconnected from ground

0

V

DD

(1/3 – 1/100)

V

OL

Logic low output voltage

I

LOAD

= 100 μA, output in open-drain mode

0.1

V

DYNAMIC PERFORMANCE

t

resp

Output response time

DAC at midscale with 10-bit resolution, FBx input at

Hi-Z, and transition step at FBx node is

(V

DAC

– 2 LSB) to (V

DAC

+ 2 LSB), transition time

measured between 10% and 90% of output, output

current of 100 µA, comparator output configured in

push-pull mode, load capacitor at DAC output is

25 pF

10

µs

(1)

Specified by design and characterization, not production tested.

(2)

This specification does not include the total unadjusted error (TUE) of the DAC.

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

8

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: