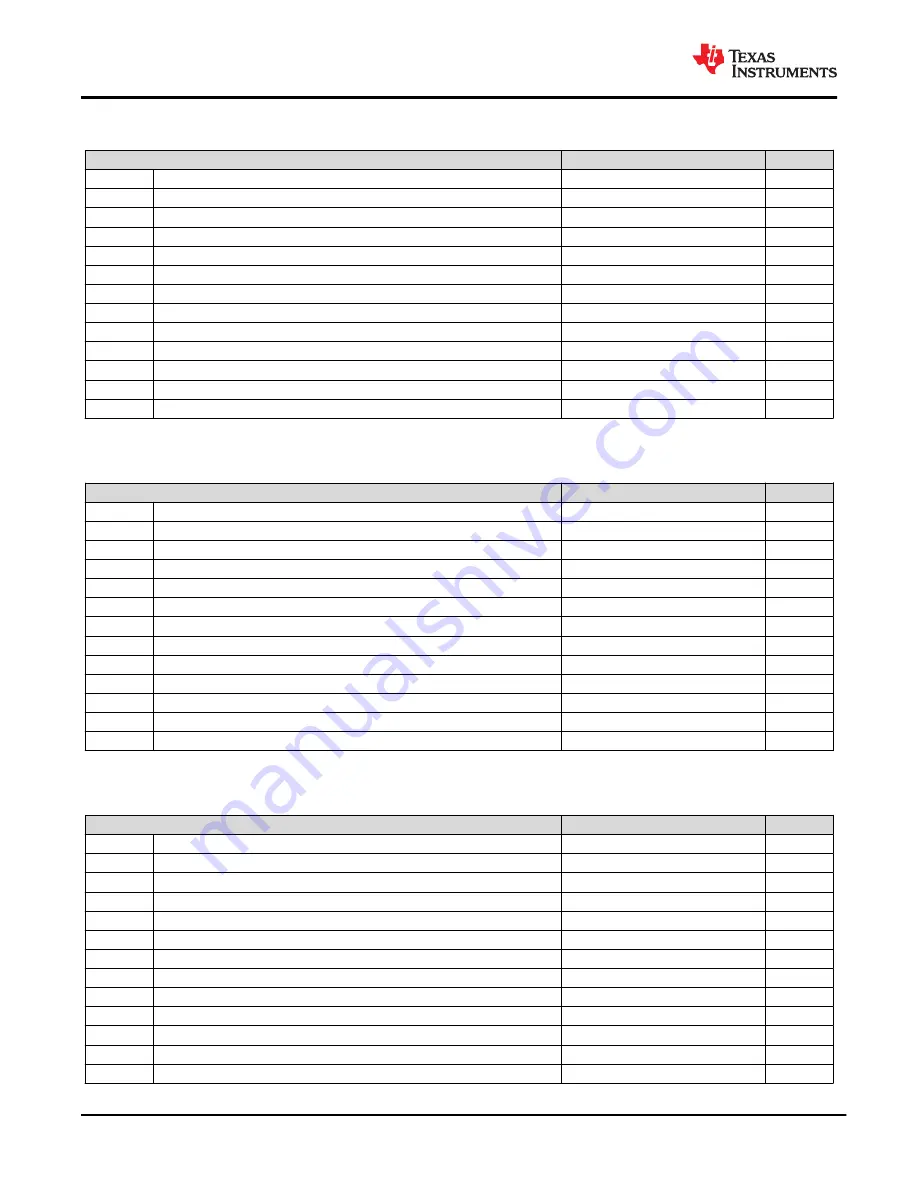

6.9 Timing Requirements: I

2

C Standard Mode

all input signals are timed from VIL to 70% of V

pull-up

, 1.7 V ≤ V

DD

≤ 5.5 V, –40°C ≤ T

A

≤ +125°C, and 1.7 V ≤ V

pull-up

≤ V

DD

V

MIN

NOM

MAX

UNIT

f

SCLK

SCL frequency

100

kHz

t

BUF

Bus free time between stop and start conditions

4.7

µs

t

HDSTA

Hold time after repeated start

4

µs

t

SUSTA

Repeated start setup time

4.7

µs

t

SUSTO

Stop condition setup time

4

µs

t

HDDAT

Data hold time

0

ns

t

SUDAT

Data setup time

250

ns

t

LOW

SCL clock low period

4700

ns

t

HIGH

SCL clock high period

4000

ns

t

F

Clock and data fall time

300

ns

t

R

Clock and data rise time

1000

ns

t

VD_DAT

Data valid time

3.45

µs

t

VD_ACK

Data valid acknowledge time

3.45

µs

6.10 Timing Requirements: I

2

C Fast Mode

all input signals are timed from VIL to 70% of V

pull-up

, 1.7 V ≤ V

DD

≤ 5.5 V, –40°C ≤ T

A

≤ +125°C, and 1.7 V ≤ V

pull-up

≤ V

DD

V

MIN

NOM

MAX

UNIT

f

SCLK

SCL frequency

400

kHz

t

BUF

Bus free time between stop and start conditions

1.3

µs

t

HDSTA

Hold time after repeated start

0.6

µs

t

SUSTA

Repeated start setup time

0.6

µs

t

SUSTO

Stop condition setup time

0.6

µs

t

HDDAT

Data hold time

0

ns

t

SUDAT

Data setup time

100

ns

t

LOW

SCL clock low period

1300

ns

t

HIGH

SCL clock high period

600

ns

t

F

Clock and data fall time

300

ns

t

R

Clock and data rise time

300

ns

t

VD_DAT

Data valid time

0.9

µs

t

VD_ACK

Data valid acknowledge time

0.9

µs

6.11 Timing Requirements: I

2

C Fast Mode Plus

all input signals are timed from VIL to 70% of V

pull-up

, 1.7 V ≤ V

DD

≤ 5.5 V, –40°C ≤ T

A

≤ +125°C, and 1.7 V ≤ V

pull-up

≤ V

DD

V

MIN

NOM

MAX

UNIT

f

SCLK

SCL frequency

1

MHz

t

BUF

Bus free time between stop and start conditions

0.5

µs

t

HDSTA

Hold time after repeated start

0.26

µs

t

SUSTA

Repeated start setup time

0.26

µs

t

SUSTO

Stop condition setup time

0.26

µs

t

HDDAT

Data hold time

0

ns

t

SUDAT

Data setup time

50

ns

t

LOW

SCL clock low period

0.5

µs

t

HIGH

SCL clock high period

0.26

µs

t

F

Clock and data fall time

120

ns

t

R

Clock and data rise time

120

ns

t

VD_DAT

Data valid time

0.45

µs

t

VD_ACK

Data valid acknowledge time

0.45

µs

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

10

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: