7 Detailed Description

7.1 Overview

The 12-bit single-channel DAC63001, 12-bit dual-channel DAC63002, 10-bit single-channel DAC53001, and

10-bit dual-channel DAC53002 (collectively referred to as the DACx300x) are a pin-compatible family of ultra-

low-power, buffered voltage-output and current-output, smart digital-to-analog converters (DACs). The DAC

channels are independently configurable as voltage output or current output. The DAC outputs change to Hi-Z

when VDD is off; a feature useful in voltage-margining applications. These smart DACs contain nonvolatile

memory (NVM), an internal reference, automatically detectable I

2

C or SPI interface, PMBus-compatibility in

I

2

C mode, a force-sense output, and a general-purpose input/output. These devices support Hi-Z power-down

modes by default, which can also be configured to 10 kΩ-GND or 100 kΩ-GND using the NVM. The DACx300x

have a power-on-reset (POR) circuit that makes sure all the registers start with default or user-programmed

settings using NVM. The DACx300x operate with either an internal reference, external reference, or with a power

supply as the reference, and provide a full-scale output between 1.8 V and 5.5 V.

The DACx300x devices support I

2

C standard mode (100 kbps), fast mode (400 kbps), and fast mode plus

(1 Mbps). The I

2

C interface can be configured with four target addresses using the A0 pin. These devices also

support specific PMBus commands such as

turn on/off

,

margin high or low

, and more. SPI mode supports

a three-wire interface by default, with up to a 50-MHz SCLK input. The GPIO input can be configured as

SDO in the NVM for SPI read capability. The GPIO input can also be configured as FAULT-DUMP, LDAC,

PD, PROTECT, RESET, and STATUS functions. These devices support deep-sleep mode in addition to sleep

(power-down) mode. Deep-sleep mode, in which the device draws a very-low power-down current of 3 μA,

uses the GPIO pin for power-down and wake up. Together with ultra-low-power operation, the DACx300x are

designed for battery-operated applications, such as land mobile radios, medical pulse oximeters, and laptops.

The DACx300x also include digital slew rate control, and support standard waveform generation such as

sine

,

cosine

,

triangular

, and

sawtooth

. These devices can generate pulse-width modulation (PWM) output with the

combination of the triangular or sawtooth waveform and the FB pin. The force-sense outputs of the DAC

channels can be used as programmable comparators. Comparator mode allows programmable hysteresis,

latching comparator, and window comparator. These features enable the DACx300x to go beyond the limitations

of a conventional DAC that depends on a processor to function. As a result of

processor-less

operation and the

smart

feature set, the DACx300x are called smart DACs.

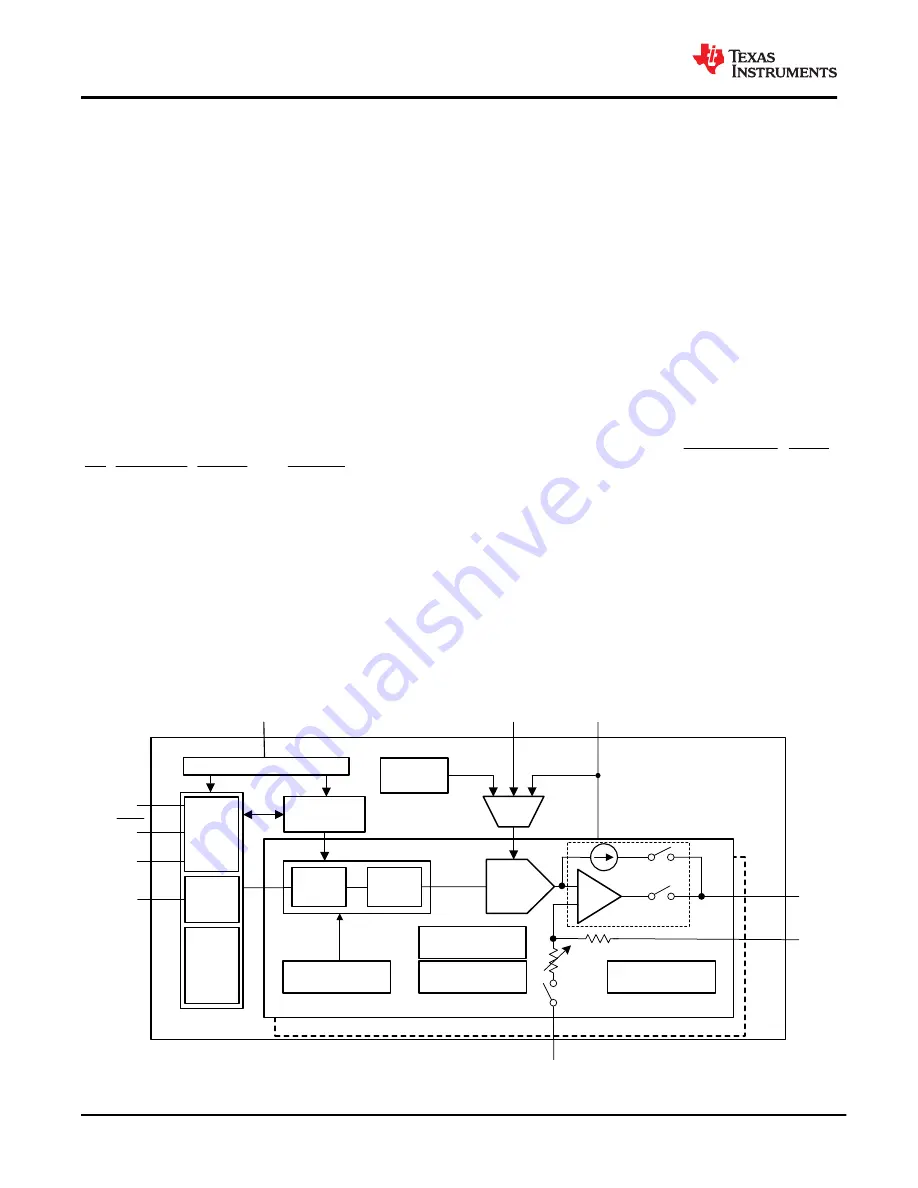

7.2 Functional Block Diagram

DAC

Register

DAC

Buffer

BUF

Power Down Logic

I

2

C / SPI

Interface

Power On Reset

AGND

VDD

DAC

Internal

Reference

Nonvolatile

Memory

CAP

LDO

+

-

R2

FB0-1

OUT0-1

GPIO/SDO

GPIO

Handle

r

GPIO

Configur

ation

A0/SDI

SCL/SYNC

SDA/SCLK

VREF

R1

Channel 0

Output

Configuration

Function Generation

MUX

Channel 1

Figure 7-1. Functional Block Diagram

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

26

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: