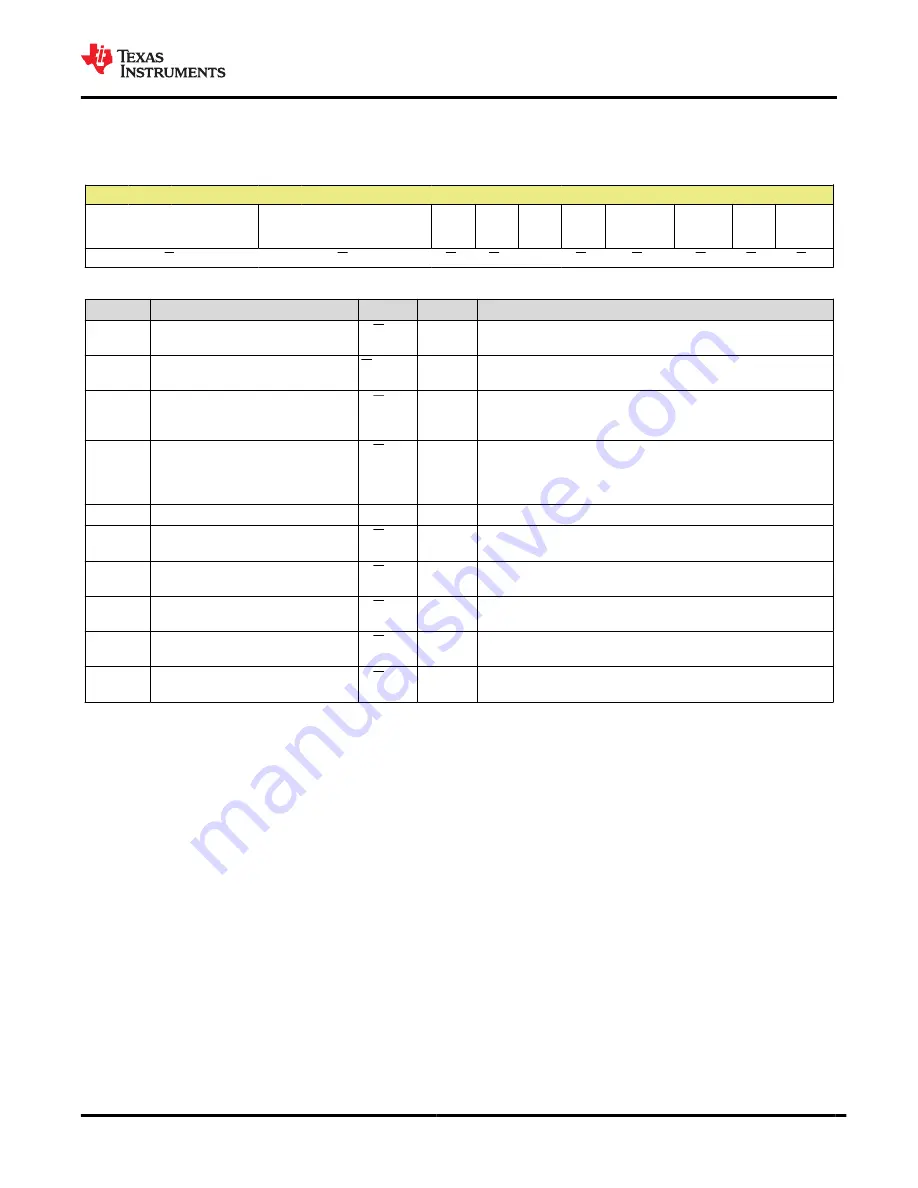

7.6.10 COMMON-TRIGGER Register (address = 20h) [reset = 0000h]

PMBus page address = FFh, PMBus register address = E4h

Figure 7-31. COMMON-TRIGGER Register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DEV-UNLOCK

RESET

LDAC

CLR

X

FAULT-

DUMP

PROTECT

READ-

ONE-

TRIG

NVM-

PROG

NVM-

RELOAD

R/W-0h

R/W-0h

R/W-0h R/W-0h

X-0h

R/W-0h

R/W-0h

R/W-0h

R/W-0h

R/W-0h

Table 7-34. COMMON-TRIGGER Register Field Descriptions

Bit

Field

Type

Reset

Description

15-12

DEV-UNLOCK

R/W

0000

0101: Device unlocking password

Others: Don't care

11-8

RESET

W

0000

1010: POR reset triggered. This bit self-resets.

Others: Don't care

7

LDAC

R/W

0

0: LDAC operation not triggered

1: LDAC operation triggered if the respective SYNC-CONFIG-X

bit in the DAC-X-FUNC-CONFIG register is 1. This bit self-resets.

6

CLR

R/W

0

0: DAC registers and outputs unaffected

1: DAC registers and outputs set to zero-code or mid-code based

on the respective CLR-SEL-X bit in the DAC-X-FUNC-CONFIG

register. This bit self-resets.

5

X

X

0

Don't care

4

FAULT-DUMP

R/W

0

0: Fault-dump is not triggered

1: Triggers fault-dump sequence. This bit self-resets.

3

PROTECT

R/W

0

0: PROTECT function not triggered

1: Trigger PROTECT function. This bit is self-resetting.

2

READ-ONE-TRIG

R/W

0

0: Fault-dump read not triggered

1: Read one row of NVM for fault-dump. This bit self-resets.

1

NVM-PROG

R/W

0

0: NVM write not triggered

1: NVM write triggered. This bit self-resets.

0

NVM-RELOAD

R/W

0

0: NVM reload not triggered

1: Reload data from NVM to register map. This bit self-resets.

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

Copyright © 2022 Texas Instruments Incorporated

63

Product Folder Links: