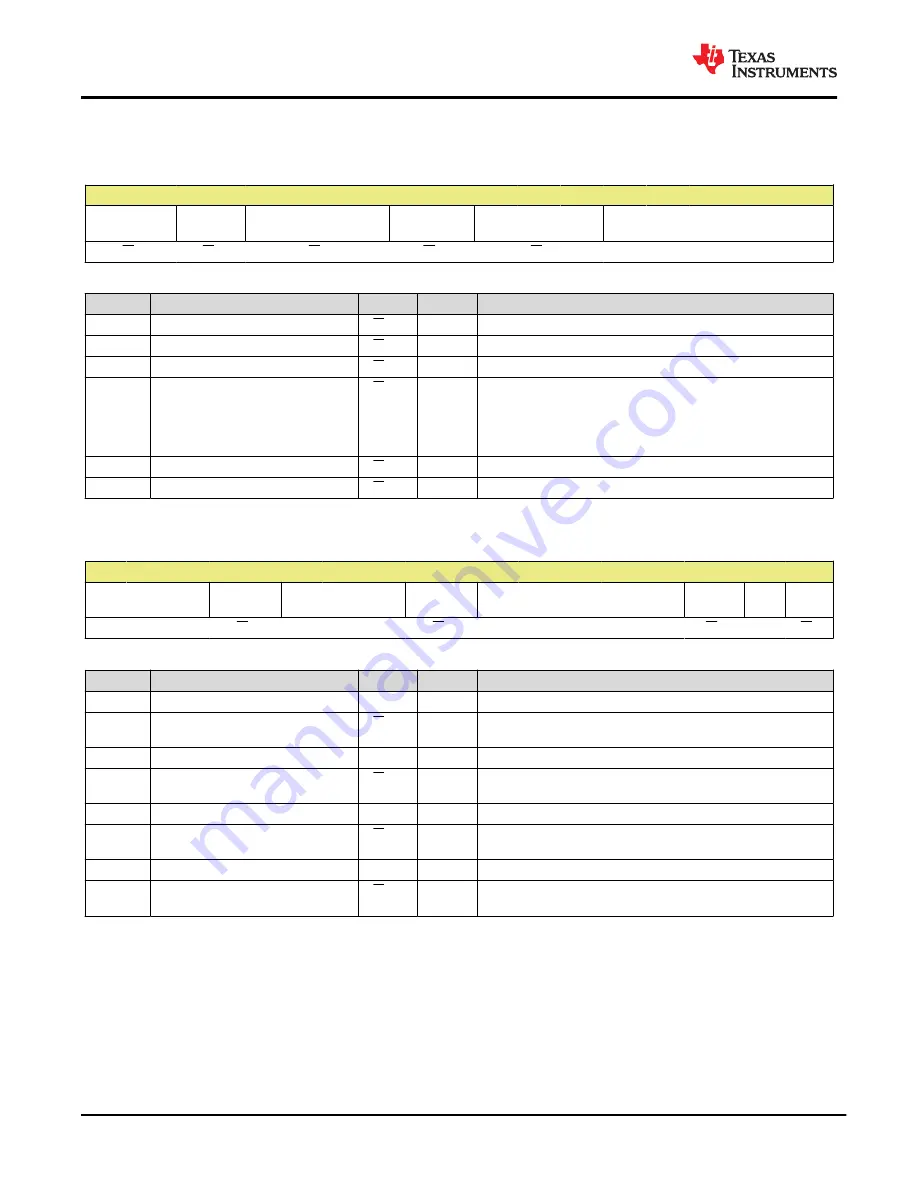

7.6.15 DEVICE-MODE-CONFIG Register (address = 25h) [reset = 0000h]

PMBus page address = FFh, PMBus register address = E9h

Figure 7-36. DEVICE-MODE-CONFIG Register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RESERVED

DIS-

MODE-IN

RESERVED

PROTECT-

CONFIG

RESERVED

X

R/W-0h

R/W-0h

R/W-0h

R/W-0h

R/W-0h

X-0h

Table 7-39. DEVICE-MODE-CONFIG Register Field Descriptions

Bit

Field

Type

Reset

Description

15-14

RESERVED

R/W

00

Always write 0b00

13

DIS-MODE-IN

R/W

0

Write 1 to this bit for low-power consumption.

12-10

RESERVED

R/W

0

Always write 0b000

9-8

PROTECT-CONFIG

R/W

00

00: Switch to Hi-Z power-down (no slew)

01: Switch to DAC code stored in NVM (no slew) and then switch

to Hi-Z power-down

10: Slew to margin-low code and then switch to Hi-Z power-down

11: Slew to margin-high code and then switch to Hi-Z power-down

7-5

RESERVED

R/W

0

Always write 0b000

4-0

X

R/W

00h

Don't care

7.6.16 INTERFACE-CONFIG Register (address = 26h) [reset = 0000h]

Figure 7-37. INTERFACE-CONFIG Register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

X

TIMEOUT-

EN

X

EN-PMBUS

X

FSDO-

EN

X

SDO-

EN

X-0h

R/W-0h

X-0h

R/W-0h

X-0h

R/W-0h

X-0h R/W-0h

Table 7-40. INTERFACE-CONFIG Register Field Descriptions

Bit

Field

Type

Reset

Description

15-13

X

X

0h

Don't care

12

TIMEOUT-EN

R/W

0

0: I

2

C timeout disabled

1: I

2

C timeout enabled

11-9

X

X

0h

Don't care

8

EN-PMBUS

R/W

0

0: PMBus disabled

1: Enable PMBus

7-3

X

X

00h

Don't care

2

FSDO-EN

R/W

0

0: Fast SDO disabled

1: Fast SDO enabled

1

X

X

0

Don't care

0

SDO-EN

R/W

0

0: SDO disabled

1: SDO enabled on GPIO pin

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

68

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: