Device

Package

Type

Package

Drawing

Pins

SPQ

Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0

(mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

(mm)

Pin1

Quadrant

OR

MSP430FG4618IZQWT

BGA MI

CROSTA

R JUNI

OR

ZQW

113

250

330.0

16.4

7.3

7.3

1.5

12.0

16.0

Q1

MSP430FG4619IPZR

LQFP

PZ

100

1000

330.0

24.4

17.4

17.4

2.0

20.0

24.0

Q2

MSP430FG4619IZQWR

BGA MI

CROSTA

R JUNI

OR

ZQW

113

2500

330.0

16.4

7.3

7.3

1.5

12.0

16.0

Q1

MSP430FG4619IZQWT

BGA MI

CROSTA

R JUNI

OR

ZQW

113

250

330.0

16.4

7.3

7.3

1.5

12.0

16.0

Q1

*All dimensions are nominal

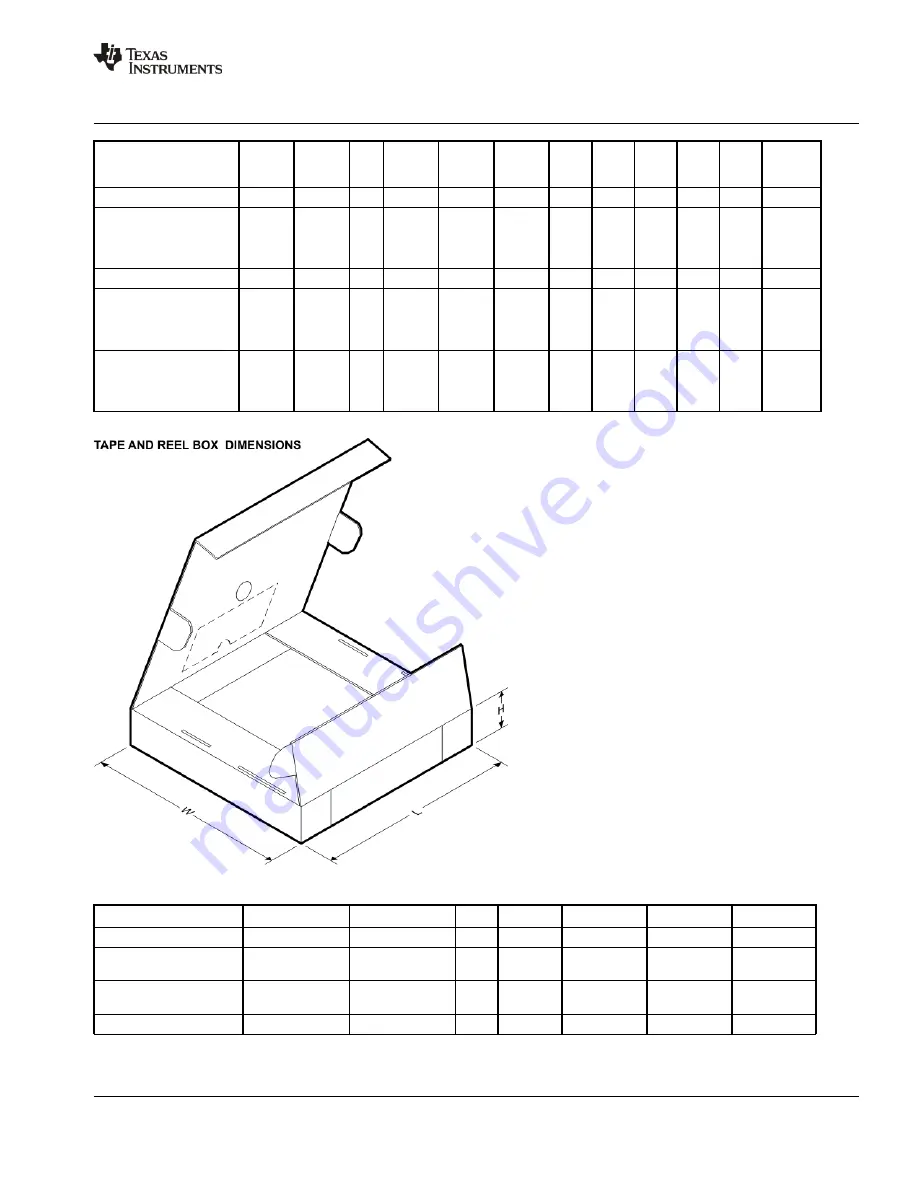

Device

Package Type

Package Drawing

Pins

SPQ

Length (mm)

Width (mm)

Height (mm)

MSP430FG4616IPZR

LQFP

PZ

100

1000

367.0

367.0

45.0

MSP430FG4616IZQWR

BGA MICROSTAR

JUNIOR

ZQW

113

2500

336.6

336.6

28.6

MSP430FG4616IZQWT

BGA MICROSTAR

JUNIOR

ZQW

113

250

336.6

336.6

28.6

MSP430FG4617IPZR

LQFP

PZ

100

1000

367.0

367.0

45.0

PACKAGE MATERIALS INFORMATION

www.ti.com

13-Sep-2013

Pack Materials-Page 2

Summary of Contents for MSP430CG4616IPZ

Page 110: ......