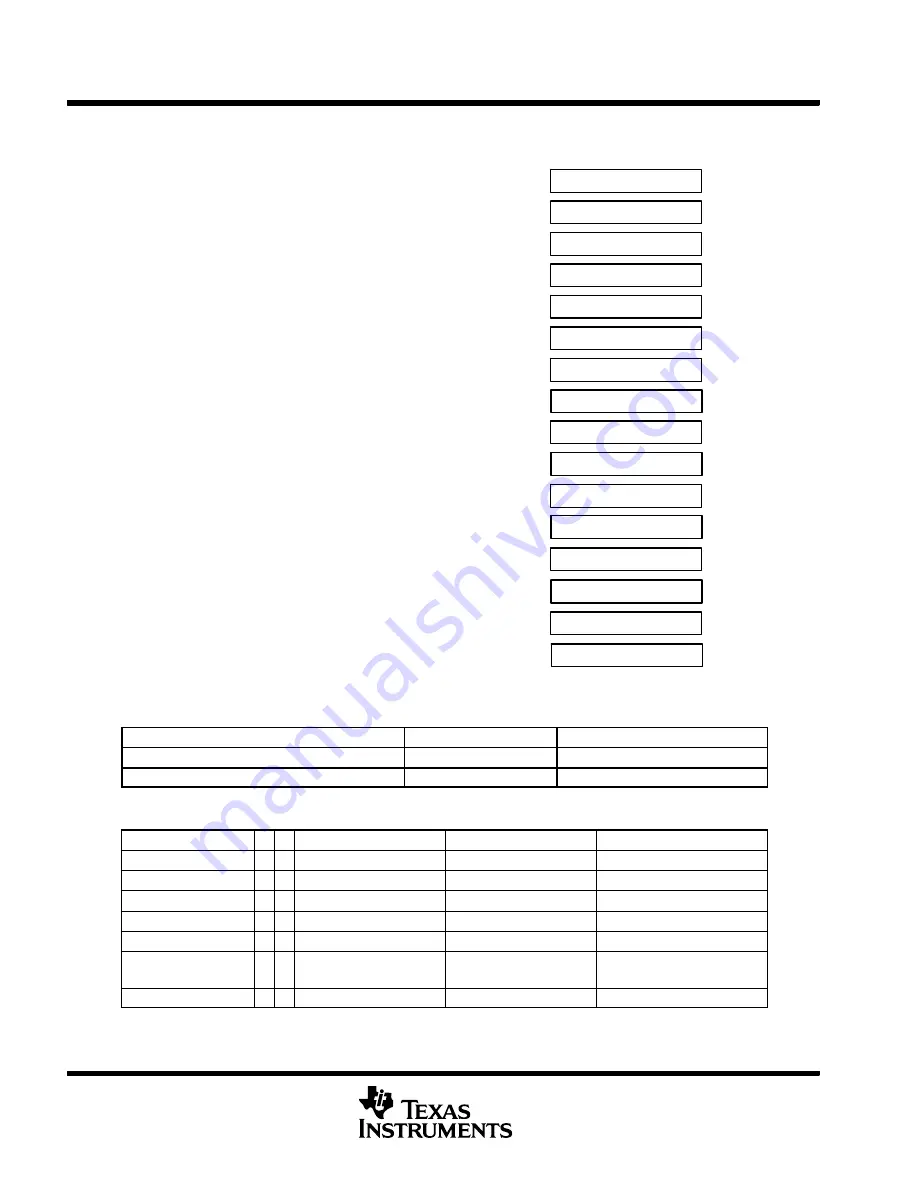

General-Purpose Register

Program Counter

Stack Pointer

Status Register

Constant Generator

General-Purpose Register

General-Purpose Register

General-Purpose Register

PC/R0

SP/R1

SR/CG1/R2

CG2/R3

R4

R5

R12

R13

General-Purpose Register

General-Purpose Register

R6

R7

General-Purpose Register

General-Purpose Register

R8

R9

General-Purpose Register

General-Purpose Register

R10

R11

General-Purpose Register

General-Purpose Register

R14

R15

MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

10

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

short-form description

CPU

The MSP430 CPU has a 16--bit RISC architecture

that is highly transparent to the application. All

operations, other than program-flow instructions,

are performed as register operations in

conjunction with seven addressing modes for

source operand and four addressing modes for

destination operand.

The CPU is integrated with 16 registers that

provide reduced instruction execution time. The

register-to-register operation execution time is

one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as

program counter, stack pointer, status register,

and constant generator, respectively. The

remaining

registers

are

general-purpose

registers.

Peripherals are connected to the CPU using data,

address, and control buses, and can be handled

with all instructions.

instruction set

The instruction set consists of 51 instructions with

three formats and seven address modes. Each

instruction can operate on word and byte data.

Table 1 shows examples of the three types of

instruction formats, and Table 2 lists the address

modes.

Table 1. Instruction Word Formats

Dual operands, source-destination

e.g., ADD R4,R5

R4 + R5 ------> R5

Single operands, destination only

e.g., CALL

R8

PC ---->(TOS), R8----> PC

Relative jump, un/conditional

e.g., JNE

Jump-on-equal bit = 0

Table 2. Address Mode Descriptions

ADDRESS MODE

S D

SYNTAX

EXAMPLE

OPERATION

Register

F F

MOV Rs,Rd

MOV R10,R11

R10 —> R11

Indexed

F F

MOV X(Rn),Y(Rm)

MOV 2(R5),6(R6)

M(2+R5)—> M(6+R6)

Symbolic (PC relative)

F F

MOV EDE,TONI

M(EDE) —> M(TONI)

Absolute

F F

MOV & MEM, & TCDAT

M(MEM) —> M(TCDAT)

Indirect

F

MOV @Rn,Y(Rm)

MOV @R10,Tab(R6)

M(R10) —> M(Tab+R6)

Indirect

autoincrement

F

MOV @Rn+,Rm

MOV @R10+,R11

M(R10) —> R11

R10 + 2—> R10

Immediate

F

MOV #X,TONI

MOV #45,TONI

#45 —> M(TONI)

NOTE: S = source

D = destination

Summary of Contents for MSP430FG47x

Page 91: ......