MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

34

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

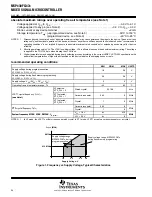

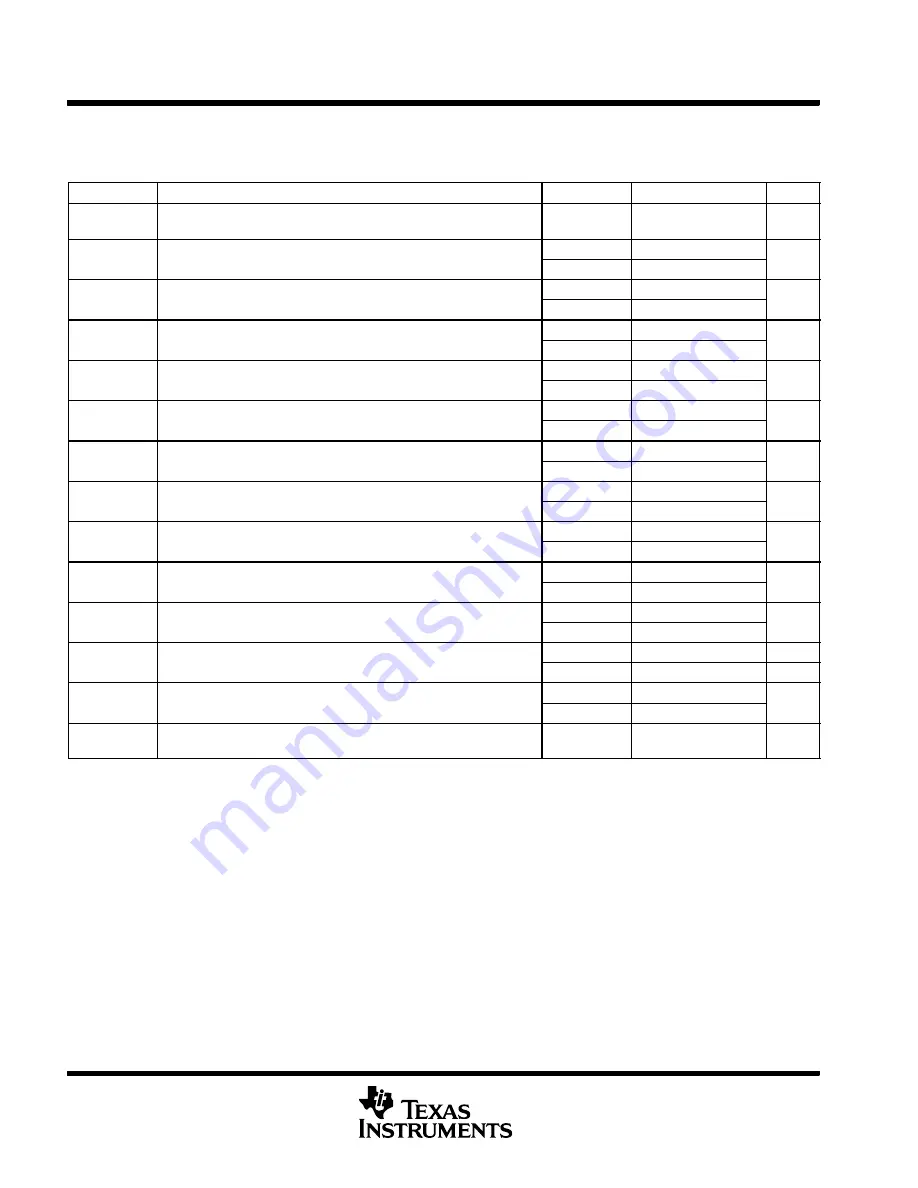

electrical characteristics over recommended operating free-air temperature (unless otherwise

noted)

DCO

PARAMETER

TEST CONDITIONS

V

CC

MIN

TYP

MAX

UNIT

f

(DCOCLK)

N

(DCO)

= 01E0h, FN_8 = FN_4 = FN_3 = FN_2 = 0, D = 2,

DCOPLUS = 0

2.2 V/3 V

1

MHz

f

FN 8 FN 4 FN 3 FN 2 0 DCOPLUS 1

2.2 V

0.3

0.65

1.25

MH

f

(DCO2)

FN_8 = FN_4 = FN_3 = FN_2 = 0 , DCOPLUS = 1

3 V

0.3

0.7

1.3

MHz

f

FN 8 FN 4 FN 3 FN 2 0 DCOPLUS 1 (see Note 1)

2.2 V

2.5

5.6

10.5

MH

f

(DCO27)

FN_8 = FN_4 = FN_3 = FN_2 = 0, DCOPLUS = 1 (see Note 1)

3 V

2.7

6.1

11.3

MHz

f

FN 8 FN 4 FN 3 0 FN 2 1 DCOPLUS 1

2.2 V

0.7

1.3

2.3

MH

f

(DCO2)

FN_8 = FN_4 = FN_3 = 0, FN_2 = 1, DCOPLUS = 1

3 V

0.8

1.5

2.5

MHz

f

FN 8 FN 4 FN 3 0 FN 2 1 DCOPLUS 1 (see Note 1)

2.2 V

5.7

10.8

18

MH

f

(DCO27)

FN_8 = FN_4 = FN_3 = 0, FN_2 = 1, DCOPLUS = 1 (see Note 1)

3 V

6.5

12.1

20

MHz

f

FN 8 FN 4 0 FN 3

1 FN 2

DCOPLUS 1

2.2 V

1.2

2

3

MH

f

(DCO2)

FN_8 = FN_4 = 0, FN_3 = 1, FN_2 = x, DCOPLUS = 1

3 V

1.3

2.2

3.5

MHz

f

FN 8 FN 4 0 FN 3

1 FN 2

DCOPLUS 1 (see Note 1)

2.2 V

9

15.5

25

MH

f

(DCO27)

FN_8 = FN_4 = 0, FN_3 = 1, FN_2 = x, DCOPLUS = 1 (see Note 1)

3 V

10.3

17.9

28.5

MHz

f

FN 8 0 FN 4

1 FN 3

FN 2

DCOPLUS 1

2.2 V

1.8

2.8

4.2

MH

f

(DCO2)

FN_8 = 0, FN_4 = 1, FN_3 = FN_2 = x, DCOPLUS = 1

3 V

2.1

3.4

5.2

MHz

f

FN 8 0 FN 4 1 FN 3

FN 2

DCOPLUS 1 (see Note 1)

2.2 V

13.5

21.5

33

MH

f

(DCO27)

FN_8 = 0, FN_4 = 1, FN_3 = FN_2 = x, DCOPLUS = 1 (see Note 1)

3 V

16

26.6

41

MHz

f

FN 8 1 FN 4 FN 3 FN 2

DCOPLUS 1

2.2 V

2.8

4.2

6.2

MH

f

(DCO2)

FN_8 = 1, FN_4 = FN_3 = FN_2 = x, DCOPLUS = 1

3 V

4.2

6.3

9.2

MHz

f

FN 8 1 FN 4 FN 3 FN 2

DCOPLUS 1 (see Note 1)

2.2 V

21

32

46

MH

f

(DCO27)

FN_8 = 1,FN_4 = FN_3 = FN_2 = x, DCOPLUS = 1 (see Note 1)

3 V

30

46

70

MHz

S

Step size between adjacent DCO taps:

1 < TAP

20

1.06

1.11

S

n

Step size between adjacent DCO taps:

S

n

= f

DCO(Tap n+1)

/ f

DCO(Tap n)

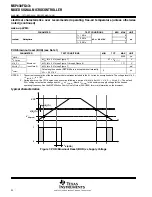

(see Figure 13 for taps 21 to 27)

TAP = 27

1.07

1.17

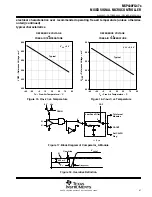

D

Temperature drift, N

(DCO)

= 01E0h, FN_8 = FN_4 = FN_3 = FN_2 = 0

2.2 V

–0.2

–0.3

–0.4

%

_

C

D

t

Temperature drift, N

(DCO)

= 01E0h, FN_8 = FN_4 = FN_3 = FN_2 = 0

D = 2, DCOPLUS = 0 (see Note 2)

3 V

–0.2

–0.3

–0.4

%

_

C

D

V

Drift with V

CC

variation, N

(DCO)

= 01E0h, FN_8 = FN_4 = FN_3 =

FN_2 = 0, D = 2, DCOPLUS = 0 (see Note 2)

0

5

15

%/V

NOTES: 1. Do not exceed the maximum system frequency.

2. This parameter is not production tested.

Summary of Contents for MSP430FG47x

Page 91: ......