MSP430FG47x

MIXED SIGNAL MICROCONTROLLER

SLAS580D -- OCTOBER 2008 -- REVISED MARCH 2011

56

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

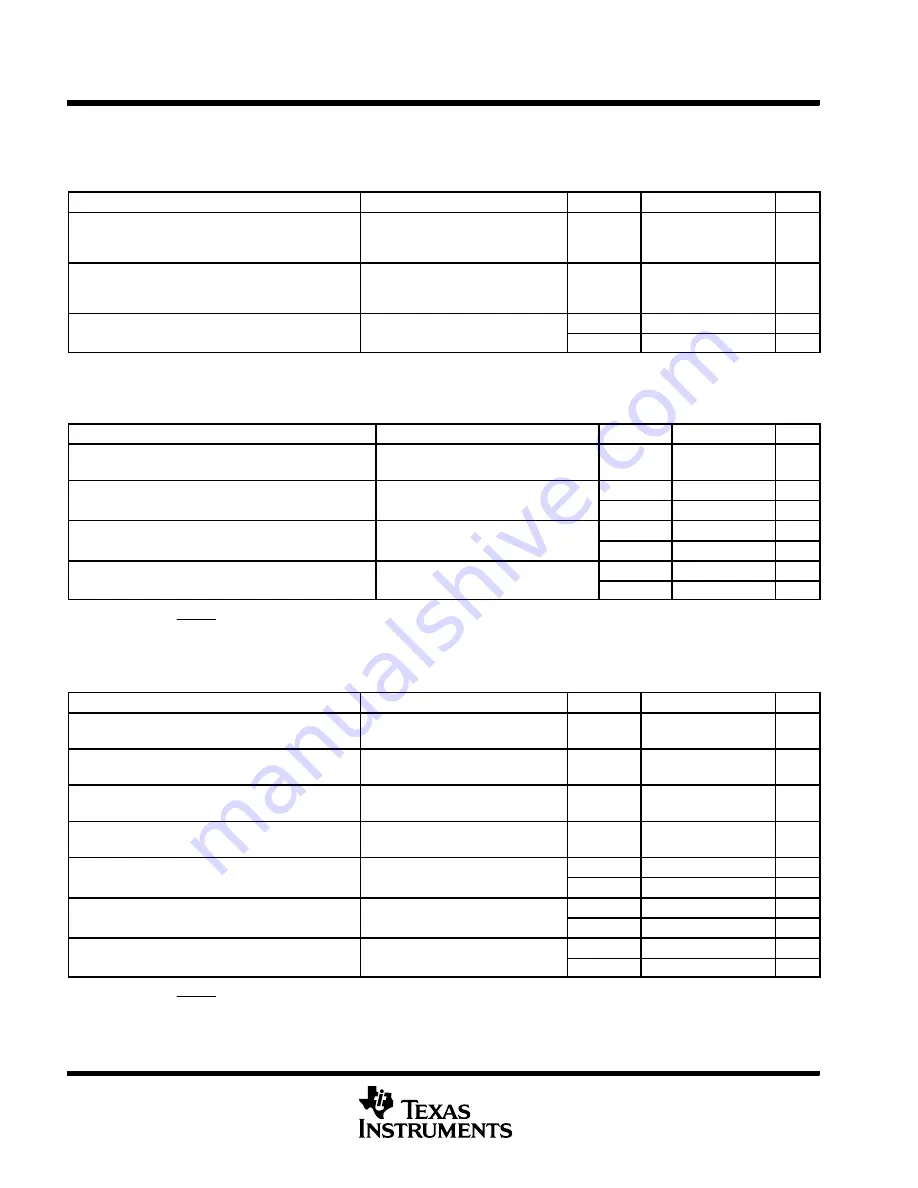

electrical characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted) (continued)

USCI (UART mode)

PARAMETER

TEST CONDITIONS

V

CC

MIN

TYP

MAX UNIT

f

USCI

USCI input clock frequency

Internal: SMCLK, ACLK

External: UCLK

Duty cycle = 50%

10%

f

SYSTEM

MHz

fmax,

BITCLK

Maximum BITCLK clock frequency

(equals baudrate in MBaud) (see

Note 1)

2.2V /3 V

2

MHz

t

UART receive deglitch time

2.2 V

50

150

ns

t

UART receive deglitch time

(see Note NO TAG)

3 V

50

100

ns

NOTES: 1. The DCO wake-up time must be considered in LPM3/4 for baudrates above 1 MHz.

2. Pulses on the UART receive input (UCxRX) shorter than the UART receive deglitch time are suppressed.

USCI (SPI master mode) (see Figure 31 and Figure 32)

PARAMETER

TEST CONDITIONS

V

CC

MIN

MAX

UNIT

f

USCI

USCI input clock frequency

SMCLK, ACLKm

Duty cycle = 50%

10%

f

SYSTEM

MHz

t

SOMI input data setup time

2.2 V

110

ns

t

SU,MI

SOMI input data setup time

3 V

75

ns

t

SOMI input data hold time

2.2 V

0

ns

t

HD,MI

SOMI input data hold time

3 V

0

ns

t

SIMO output data valid time

UCLK edge to SIMO valid C

20 pF

2.2 V

30

ns

t

VALID,MO

SIMO output data valid time

UCLK edge to SIMO valid, C

L

= 20 pF

3 V

20

ns

NOTE:

f

UCxCLK

=

1

2t

LO

∕

HI

with

t

LO

∕

HI

≥

max(t

VALID,MO(USCI)

+

t

SU,SI(Slave),

t

SU,MI(USCI)

+

t

VALID,SO(Slave)

)

.

For the slave’s parameters t

SU,SI(Slave)

and t

VALID,SO(Slave)

refer to the SPI parameters of the attached slave.

USCI (SPI slave mode) (see Figure 33 and Figure 34)

PARAMETER

TEST CONDITIONS

V

CC

MIN

TYP

MAX UNIT

t

STE,LEAD

STE lead time

STE low to clock

2.2 V/3 V

50

ns

t

STE,LAG

STE lag time

Last clock to STE high

2.2 V/3 V

10

ns

t

STE,ACC

STE access time

STE low to SOMI data out

2.2 V/3 V

50

ns

t

STE,DIS

STE disable time

STE high to SOMI high impedance

2.2 V/3 V

50

ns

t

SIMO inp t data set p time

2.2 V

20

ns

t

SU,SI

SIMO input data setup time

3 V

15

ns

t

SIMO inp t data hold time

2.2 V

10

ns

t

HD,SI

SIMO input data hold time

3 V

10

ns

t

SOMI o tp t data alid time

UCLK edge to SOMI valid,

2.2 V

75

110

ns

t

VALID,SO

SOMI output data valid time

UCLK edge to SOMI valid,

C

L

= 20 pF

3 V

50

75

ns

NOTE:

f

UCxCLK

=

1

2t

LO

∕

HI

with

t

LO

∕

HI

≥

max(t

VALID,MO(Master)

+

t

SU,SI(USCI),

t

SU,MI(Master)

+

t

VALID,SO(USCI)

)

.

For the master’s parameters t

SU,MI(Master)

and t

VALID,MO(Master)

refer to the SPI parameters of the attached master.

Summary of Contents for MSP430FG47x

Page 91: ......