Individual Instruction Descriptions

4-160

4.14.65

SHL

Shift Left

Syntax

[label]

name

dest [, mod]

Clock,

clk

Word,

w

With RPT,

clk

Class

SHL

A

n[~] [, next A]

1

1

n

R

+3

3

Execution

[premodify AP if

mod specified]

PH, PL

⇐

src << SV

PC

⇐

PC + 1

Flags Affected

OF, SF, ZF, CF are set accordingly

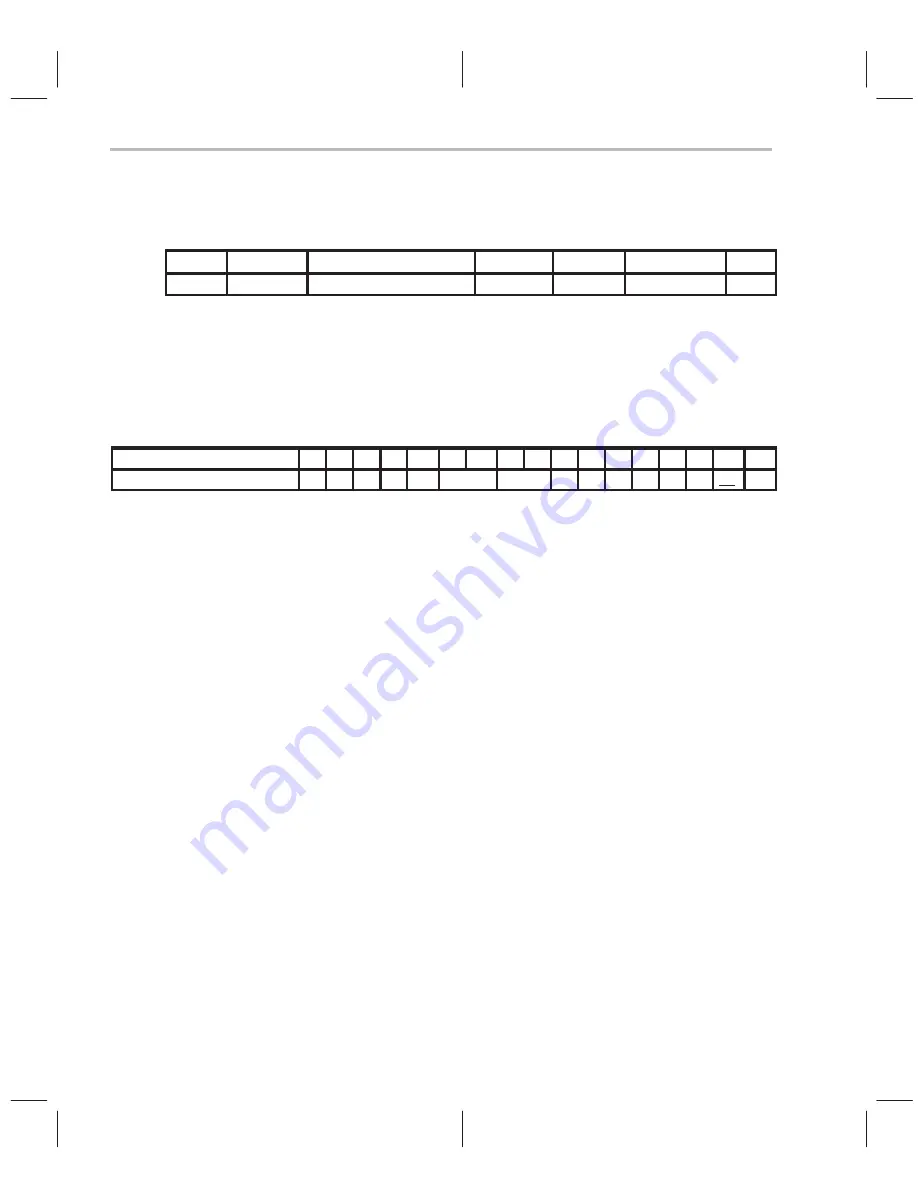

Opcode

Instructions

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SHL A

n[~] [, next A]

1

1

1

0

0

next A

A

n

1

1

1

1

1

0

A~

0

Description

Premodify the accumulator pointer if specified. Shift accumulator word left n

SV

bits (as specified by the SV register) into a 32-bit result. This result is zero-filled

or sign-extended on the left (based on the setting of the extended sign mode

(XM) bit in the status register). The upper 16 bits are latched into the PH

register. Accumulator content is not changed. The lower 16-bit value, PL, is

discarded. The SHL instruction can be used with a RPT instruction, but without

much advantage since the instruction does not write back into the

accumulator. Use SHLAC for this purpose.

See Also

SHLS

Example 4.14.65.1

SHL A0, ++A

Preincrement accumulator pointer AP0. Shift accumulator word A0 to the left by SV bits. Accumulator

content is not changed. PH contains the upper 16 bits of the shifted result.

Summary of Contents for MSP50C614

Page 1: ...MSP50C614 Mixed Signal Processor User s Guide SPSU014 January 2000 Printed on Recycled Paper ...

Page 6: ...vi ...

Page 92: ...3 22 ...

Page 300: ...Instruction Set Summay 4 208 Assembly Language Instructions ...

Page 314: ...Software Emulator 5 14 Figure 5 13 Project Menu Figure 5 14 Project Open Dialog ...

Page 325: ...Software Emulator 5 25 Code Development Tools Figure 5 25 EPROM Programming Dialog ...

Page 331: ...Software Emulator 5 31 Code Development Tools Figure 5 31 Context Sensitive Help System ...

Page 368: ...5 68 ...

Page 394: ...7 12 ...

Page 402: ...A 8 ...

Page 412: ...Packaging B 10 ...