Architecture

B-6

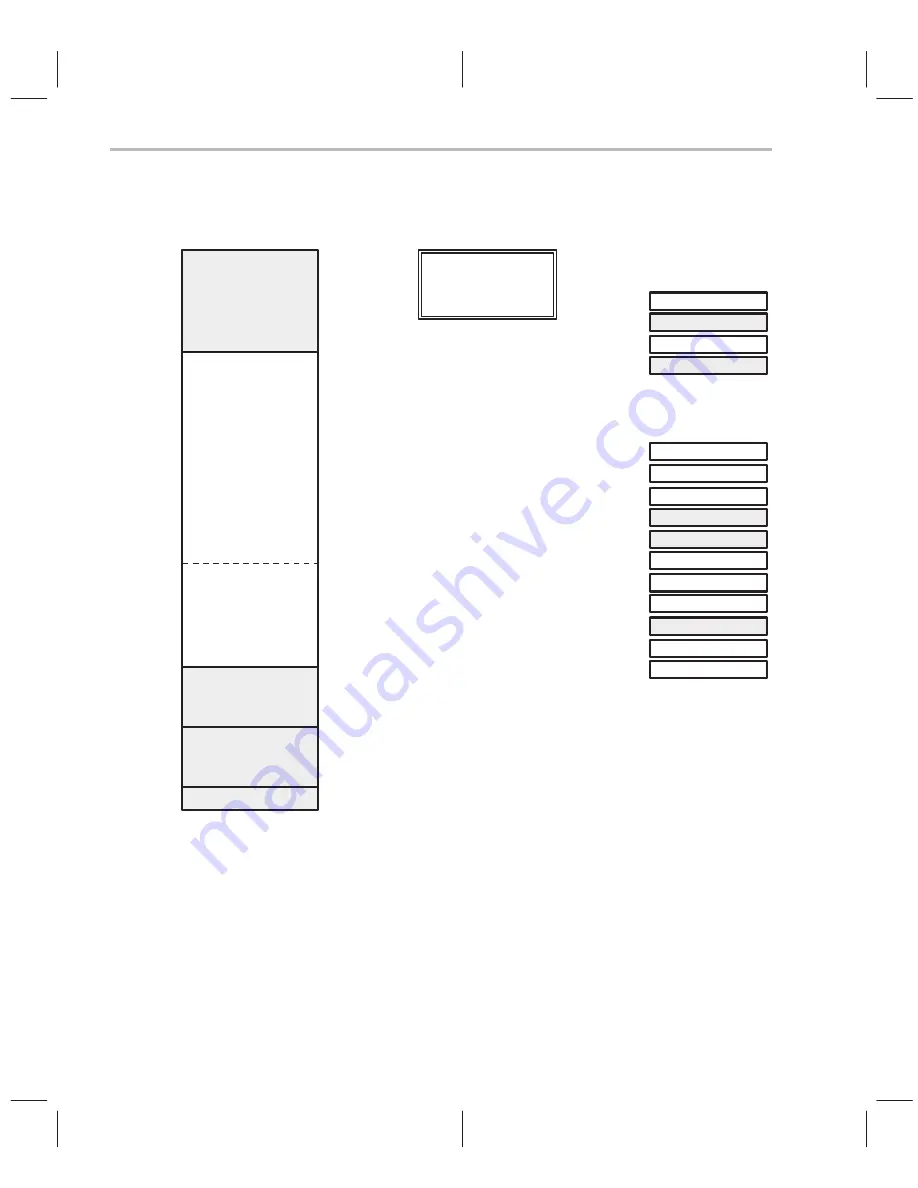

Figure B–2. MSP50C604 Memory Organization and I/O ports

0x0000

0x0800

0x07FF

0x7FF0

0x7FF7

User ROM

30704 x 17 bit

(C604 : read–only)

(P614 : EPROM)

Internal Test Code

2048 x 17 bit

(reserved )

Program Memory

Peripheral Ports

0x 027F

0x 0000

Data Memory

RAM

640 x 17 bit

Macro Call Vectors

255 x 17 bit

(overlaps interrupt

vector locations)

0x 10

PC

0..7

data

PC

0..7

ctrl

PD

0..7

data

PD

0..7

ctrl

0x 2C

0x 30

0x 34

0x 38

PG

0

0x 39

DAC data

0x 3A

DAC ctrl

0x 3B

IntGenCtrl

IFR

0x 3D

PRD1

0x 3E

TIM1

0x 3F

0x 14

ClkSpdCtrl

0x 18

PRD2

0x 1C

TIM2

0x7F00

0x 2F RTRIM

Usable Interrupt

Vectors

8 x 17 bit

0x7FFE

Unusable Interrupt

Vectors

(reserved)

0x7FF8

RESET vector

0x7FFF

Summary of Contents for MSP50C614

Page 1: ...MSP50C614 Mixed Signal Processor User s Guide SPSU014 January 2000 Printed on Recycled Paper ...

Page 6: ...vi ...

Page 92: ...3 22 ...

Page 300: ...Instruction Set Summay 4 208 Assembly Language Instructions ...

Page 314: ...Software Emulator 5 14 Figure 5 13 Project Menu Figure 5 14 Project Open Dialog ...

Page 325: ...Software Emulator 5 25 Code Development Tools Figure 5 25 EPROM Programming Dialog ...

Page 331: ...Software Emulator 5 31 Code Development Tools Figure 5 31 Context Sensitive Help System ...

Page 368: ...5 68 ...

Page 394: ...7 12 ...

Page 402: ...A 8 ...

Page 412: ...Packaging B 10 ...