Memory Organization: RAM and ROM

2-17

MSP50C614 Architecture

When writing to any of the locations in the I/O address map, therefore, the

bit-masking need only extend as far as width of location. Within a 16-bit

accumulator, the desired bits (width of location) should be right-justified. The

write operation is accomplished using the OUT instruction, with the address

of the I/O port as an argument.

A read from these locations is accomplished using the IN instruction, with the

address of the I/O port as an argument. When reading from the I/O port to a

16-bit accumulator, the IN instruction automatically clears any extra bits in

excess of width of location. The desired bits in the result will be right-justified

within the accumulator.

Allowable access indicates whether the port is bidirectional, read-only, or

write-only. The last column of the table points to the section in this manual

where the functions of each bit have been defined in more detail.

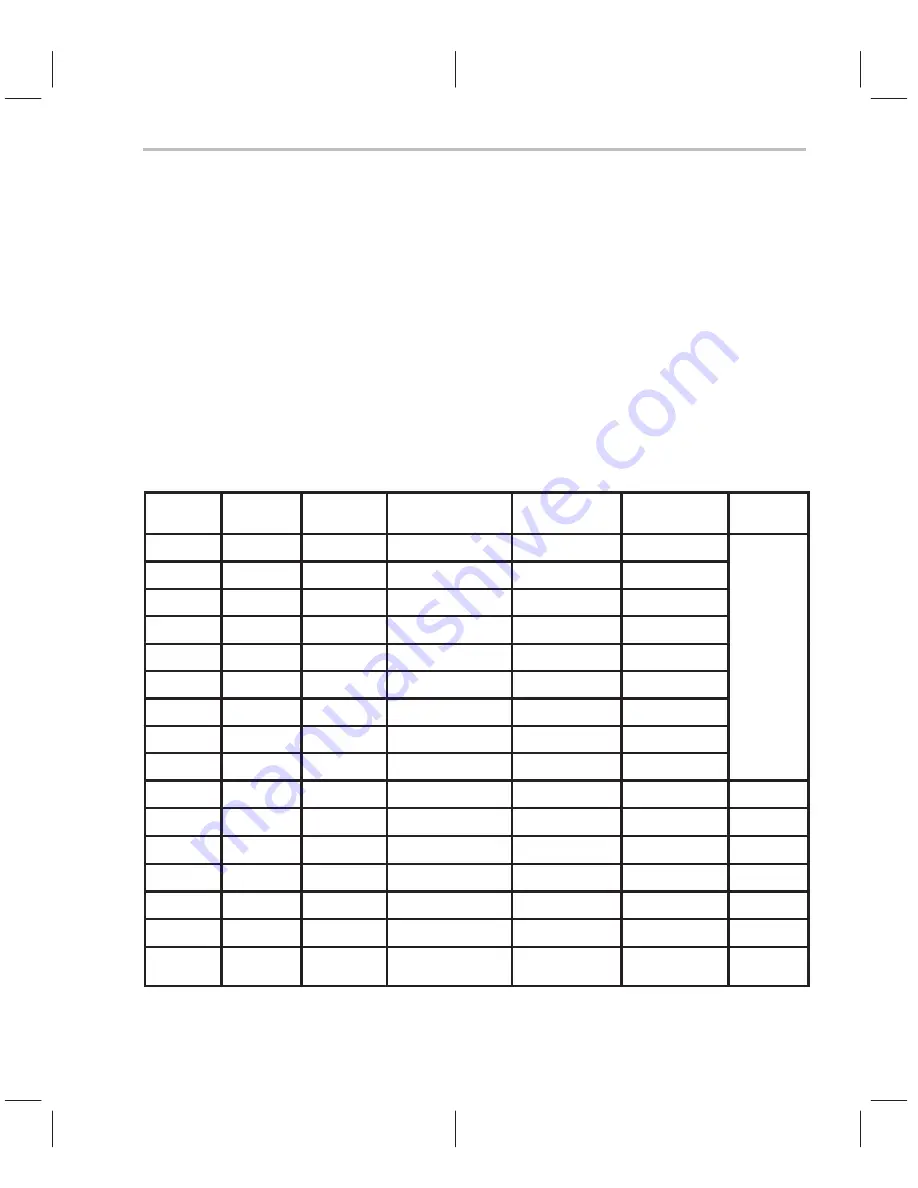

Table 2–2. Summary of C614’s Peripheral Communications Ports

I/O Map

Address

Width of

Location

Allowable

Access

Control Register

Name

Abbreviation

State after

RESET LOW

Section for

Reference

0x00

8 bits

read & write

I/O port A data

PA0..7 Data

unknown†

0x04

8 bits

read & write

I/O port A control

PA0..7 Ctrl

0x00 ‡

0x08

8 bits

read & write

I/O port B data

PB0..7 Data

unknown

0x0C

8 bits

read & write

I/O port B control

PB0..7 Ctrl

0x00

0x10

8 bits

read & write

I/O port C data

PC0..7 Data

unknown

3.1.1

0x14

8 bits

read & write

I/O port C control

PC0..7 Ctrl

0x00

0x18

8 bits

read & write

I/O port D data

PD0..7 Data

unknown

0x1C

8 bits

read & write

I/O port D control

PD0..7 Ctrl

0x00

0x20

8 bits

read & write

I/O port E data

PE0..7 Data

unknown

0x24

8 bits

read & write

I/O port E control

PE0..7 Ctrl

0x00

0x28

8 bits

READ only

Input port F data

PF0..7 Data

unknown

3.1.2

0x2C

16 bits

read & write

Output port G data

PG0..15 Data

0x0000

3.1.3

0x30

16 bits

WRITE only

DAC data

DAC Data

0x0000

3.2.2

0x34

4 bits

read & write

DAC control

DAC Ctrl

0x0

3.2.2

0x38

16 bits

read & write

Interrupt/general Ctrl

IntGenCtrl

0x0000

3.4

0x39

8 bits

read & write

Interrupt flag

IFR

Same state as

before RESET

2.7

† Input states are provided by the external hardware.

‡ A control register value of 0x00 yields a port configuration of all inputs.

Summary of Contents for MSP50C614

Page 1: ...MSP50C614 Mixed Signal Processor User s Guide SPSU014 January 2000 Printed on Recycled Paper ...

Page 6: ...vi ...

Page 92: ...3 22 ...

Page 300: ...Instruction Set Summay 4 208 Assembly Language Instructions ...

Page 314: ...Software Emulator 5 14 Figure 5 13 Project Menu Figure 5 14 Project Open Dialog ...

Page 325: ...Software Emulator 5 25 Code Development Tools Figure 5 25 EPROM Programming Dialog ...

Page 331: ...Software Emulator 5 31 Code Development Tools Figure 5 31 Context Sensitive Help System ...

Page 368: ...5 68 ...

Page 394: ...7 12 ...

Page 402: ...A 8 ...

Page 412: ...Packaging B 10 ...