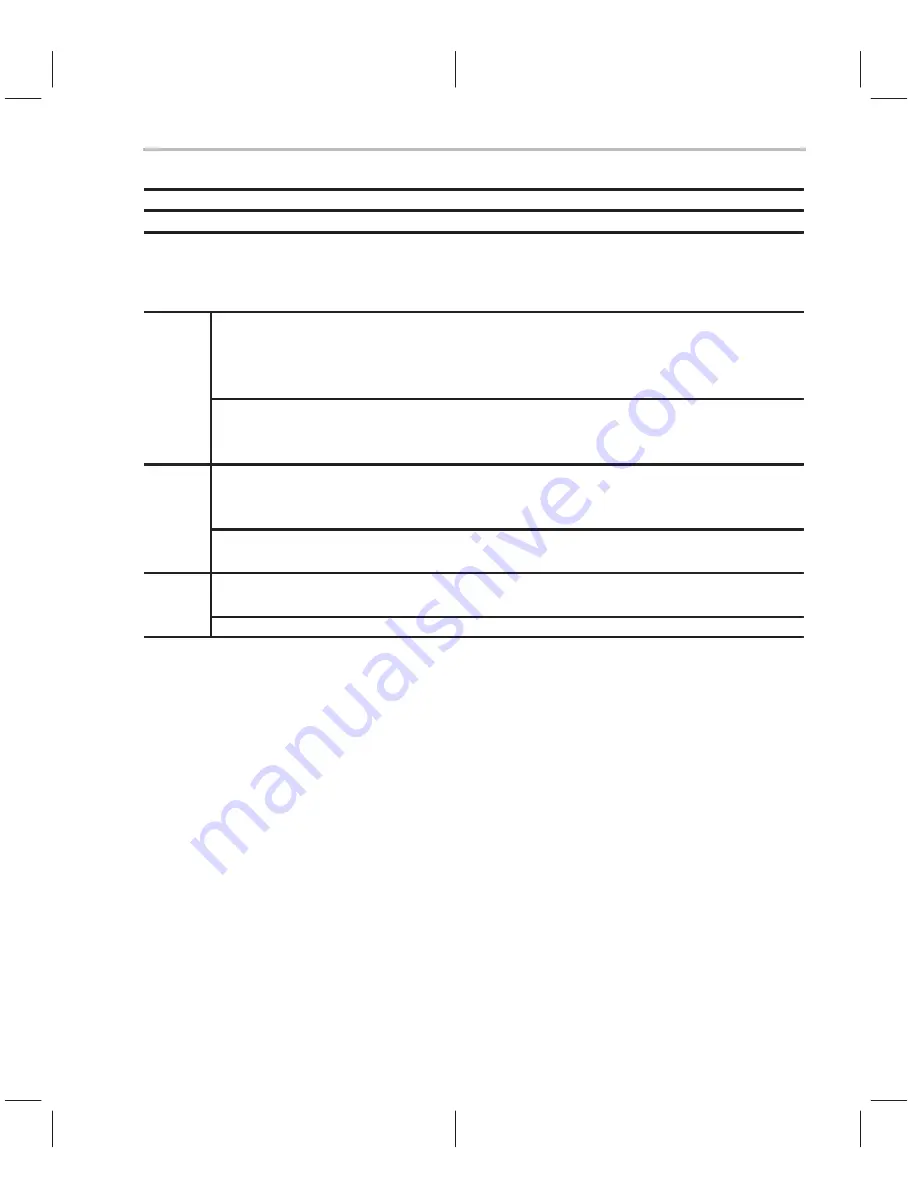

Digital-to-Analog Converter (DAC)

3-13

Peripheral Functions

10 kHz Nominal Synthesis Rate

32.768 kHz Oscillator Reference

DAC

Precision

IntGenCtrl

PDMCD

Bit

Over-

Sampling

Factor

ClkSpdCtrl

PLLM

Register

Value

(hex)

Master

Clock

Rate

(MHz)

PDM

RATE

(MHZ)

CPU

Clock

Rate

(MHz)

Output

Sampling

Rate

(kHz)

Number of

Instructs

Between

DAC

Interrupts

Number of

Instructs

Between

10 kHz

Interrupts

8 bits

1

1x

0x 13

2.62

2.62

1.31

10.24

128

128

2x

0x 26

5.11

5.11

2.56

19.97

128

256

4x

0x 4D

10.22

10.22

5.11

39.94

128

512

8x

0x 9B

20.45

20.45

10.22

79.87

128

1024

0

1x

0x 26

5.11

2.56

2.56

9.98

256

256

2x

0x 4D

10.22

5.11

5.11

19.97

256

512

4x

0x 9B

20.45

10.22

10.22

39.94

256

1024

9 bits

1

1x

0x 26

5.11

5.11

2.56

9.98

256

256

2x

0x 4D

10.22

10.22

5.11

19.97

256

512

4x

0x 9B

20.45

20.45

10.22

39.94

256

1024

0

1x

0x 4D

10.22

5.11

5.11

9.98

512

512

2x

0x 9B

20.45

10.22

10.22

19.97

512

1024

10 bits

“1”

1x

0x 4D

10.22

10.22

5.11

9.98

512

512

2x

0x 9B

20.45

20.45

10.22

19.97

512

1024

“0”

1x

0x 9B

20.45

10.22

10.22

9.98

1024

1024

Summary of Contents for MSP50C614

Page 1: ...MSP50C614 Mixed Signal Processor User s Guide SPSU014 January 2000 Printed on Recycled Paper ...

Page 6: ...vi ...

Page 92: ...3 22 ...

Page 300: ...Instruction Set Summay 4 208 Assembly Language Instructions ...

Page 314: ...Software Emulator 5 14 Figure 5 13 Project Menu Figure 5 14 Project Open Dialog ...

Page 325: ...Software Emulator 5 25 Code Development Tools Figure 5 25 EPROM Programming Dialog ...

Page 331: ...Software Emulator 5 31 Code Development Tools Figure 5 31 Context Sensitive Help System ...

Page 368: ...5 68 ...

Page 394: ...7 12 ...

Page 402: ...A 8 ...

Page 412: ...Packaging B 10 ...