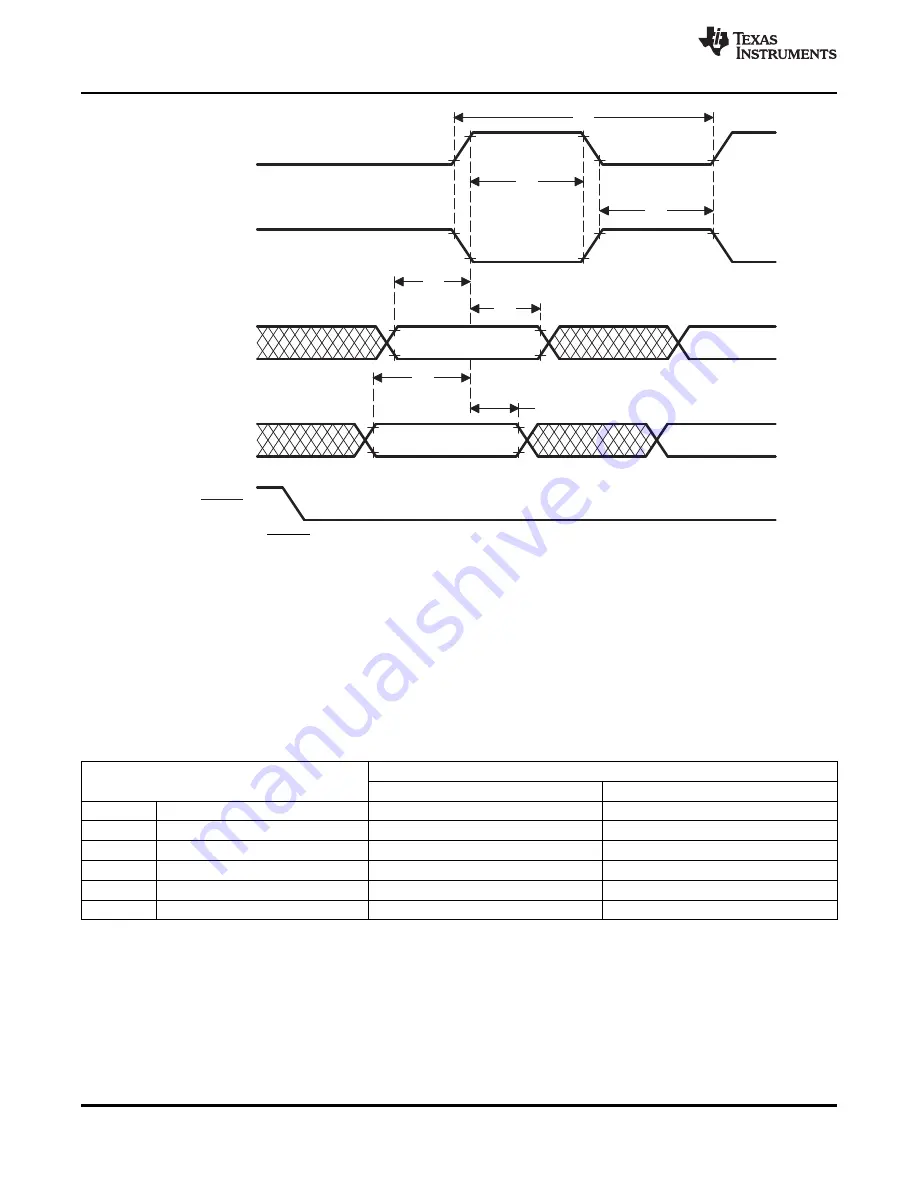

Data Valid

22

SPISIMO

SPISOMI

SPICLK

(clock polarity = 1)

SPICLK

(clock polarity = 0)

SPISIMO Data

Must Be Valid

SPISOMI Data Is Valid

21

12

18

17

14

13

SPISTE

(see Note A)

SM320F2812-HT

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

www.ti.com

A.

In the slave mode, the SPISTE signal should be asserted low at least 0.5tc(SPC) before the valid SPI clock edge and

remain low for at least 0.5tc(SPC) after the receiving edge (SPICLK) of the last data bit.

Figure 6-27. SPI Slave Mode External Timing (Clock Phase = 1)

6.21 External Interface (XINTF) Timing

Each XINTF access consists of three parts: Lead, Active, and Trail. The user configures the

Lead/Active/Trail wait states in the XTIMING registers. There is one XTIMING register for each XINTF

zone.

Table 6-25

shows the relationship between the parameters configured in the XTIMING register and

the duration of the pulse in terms of XTIMCLK cycles.

Table 6-25. Relationship Between Parameters Configured in XTIMING and Duration of Pulse

(1) (2) (3)

DURATION (ns)

DESCRIPTION

X2TIMING = 0

X2TIMING = 1

LR

Lead period, read access

XRDLEAD

×

t

c(XTIM)

(XRDLEAD

×

2)

×

t

c(XTIM)

AR

Active period, read access

(XRD WS + 1)

×

t

c(XTIM)

(XRDACTIVE

×

2 + WS + 1)

×

t

c(XTIM)

TR

Trail period, read access

XRDTRAIL

×

t

c(XTIM)

(XRDTRAIL

×

2)

×

t

c(XTIM)

LW

Lead period, write access

XWRLEAD

×

t

c(XTIM)

(XWRLEAD

×

2)

×

t

c(XTIM)

AW

Active period, write access

(XWR WS + 1) x t

c(XTIM)

(XWRACTIVE

×

2 + WS + 1)

×

t

c(XTIM)

TW

Trail period, write access

XWRTRAIL

×

t

c(XTIM)

(XWRTRAIL

×

2)

×

t

c(XTIM)

(1)

Not production tested.

(2)

t

c(XTIM)

–

Cycle time, XTIMCLK

(3)

WS refers to the number of wait states inserted by hardware when using XREADY. If the zone is configured to ignore XREADY

(USEREADY = 0), then WS = 0.

Minimum wait state requirements must be met when configuring each zone's XTIMING register. These

requirements are in addition to any timing requirements as specified by that device's data sheet. No

internal device hardware is included to detect illegal settings.

•

If the XREADY signal is ignored (USEREADY = 0), then:

1. Lead:

LR

≥

t

c(XTIM)

114

Electrical Specifications

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......