Lead 1

Active

Trail

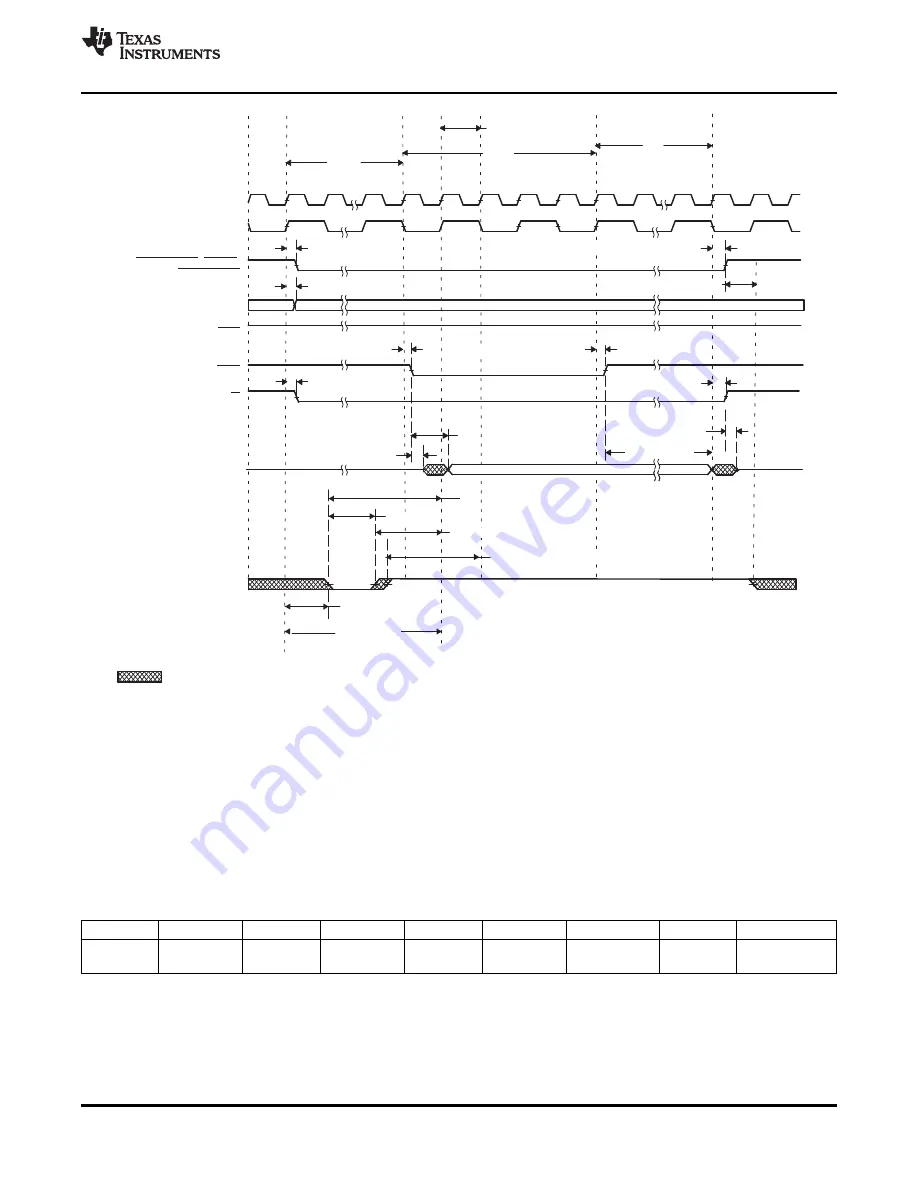

XCLKOUT = XTIMCLK

XCLKOUT = 1/2 XTIMCLK

XA[0:18]

XD[0:15]

t

d(XCOHL-XWEH)

t

d(XCOHL-XZCSH)

t

d(XCOH-XA)

WS (Asynch)

XZCS0AND1, XZCS2,

XZCS6AND7

XRD

XWE

XR/W

t

d(XCOH-XZCSL)

NOTES: A. All XINTF accesses (lead period) begin on the rising edge of XCLKOUT. When necessary, the device inserts an

alignment cycle before an access to meet this requirement.

B. During alignment cycles, all signals transitions to their inactive state.

C. During inactive cycles, the XINTF address bus always holds the last address put out on the bus. This includes alignment

cycles.

D. For each sample, setup time from the beginning of the access can be calculated as:

D = (X XWRACTIVE −3 + n) t

c(XTIM)

− t

su(XRDYasynchL)XCOHL

where n is the sample number: n = 1, 2, 3 and so forth.

E. Reference for the first sample is with respect to this point

E = (X XWRACTIVE −2) t

c(XTIM)

t

d(XCOH-XRNWL)

t

d(XCOHL-XRNWH)

t

en(XD)XWEL

t

h(XD)XWEH

t

h(XRDYasynchL)

DOUT

t

dis(XD)XRNW

t

h(XRDYasynchH)XZCSH

See Note E

See Note D

= Don’t care. Signal can be high or low during this time.

Legend:

t

su(XRDYasynchL)XCOHL

t

su(XRDYasynchH)XCOHL

t

d(XWEL-XD

)

t

d(XCOHL-XWEL)

t

e(XRDYasynchH)

XREADY(Asynch)

SM320F2812-HT

www.ti.com

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

Figure 6-34. Write With Asynchronous XREADY Access

XTIMING register parameters used for this example:

XRDLEAD

XRDACTIVE

XRDTRAIL

USEREADY

X2TIMING

XWRLEAD

XWRACTIVE

XWRTRAIL

READYMODE

1 = XREADY

N/A

(1)

N/A

(1)

N/A

(1)

1

0

≥

1

3

≥

1

(Asynch)

(1)

N/A =

"

Don

'

t care

"

for this example

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Electrical Specifications

127

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......