Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

Bit 0

Bit(n-1)

(n-2)

(n-3)

(n-4)

CLKX

FSX

DX

M30

M31

DR

M28

M24

M29

M25

LSB

MSB

M32

M33

SM320F2812-HT

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

www.ti.com

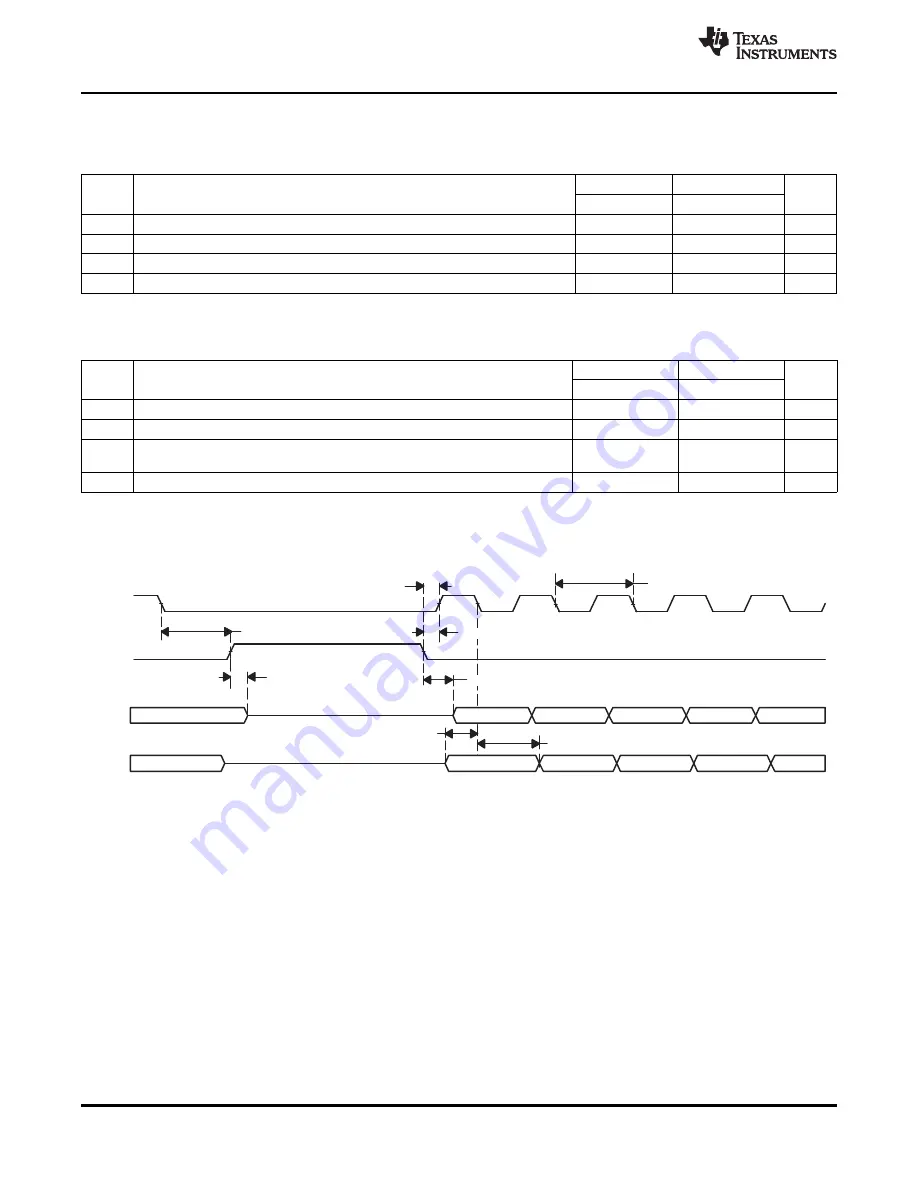

6.30.2 McBSP as SPI Master or Slave Timing

Table 6-54. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)

(1)

MASTER

SLAVE

NO.

UNIT

MIN

MAX

MIN

MAX

M30

t

su(DRV0CKXL)

Setup time, DR valid before CLKX low

P

–

10

8P

–

10

ns

M31

t

h(CKXL0DRV)

Hold time, DR valid after CLKX low

P

–

10

8P

–

10

ns

M32

t

su(BFXL0CKXH)

Setup time, FSX low before CLKX high

8P + 10

ns

M33

t

c(CKX)

Cycle time, CLKX

2P

16P

ns

(1)

Not production tested.

Table 6-55. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0)

(1) (2)

MASTER

SLAVE

NO.

PARAMETER

UNIT

MIN

MAX

MIN

MAX

M24

t

h(CKXL0FXL)

Hold time, FSX low after CLKX low

2P

ns

M25

t

d(FXL0CKXH)

Delay time, FSX low to CLKX high

P

ns

Disable time, DX high impedance following last data bit from

M28

t

dis(FXH0DXHZ)

6

6P + 6

ns

FSX high

M29

t

d(FXL0DXV)

Delay time, FSX low to DX valid

6

4P + 6

ns

(1)

Not production tested.

(2)

2P = 1/CLKG

For all SPI slave modes, CLKX has to be minimum eight CLKG cycles. Also, CLKG should be LSPCLK/2 by setting CLKSM = CLKGDV

= 1. With maximum LSPCLK speed of 75 MHz, CLKX maximum frequency is LSPCLK/16, that is 4.5 MHz and P = 13.3 ns.

Figure 6-43. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0

142

Electrical Specifications

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......