SM320F2812-HT

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

www.ti.com

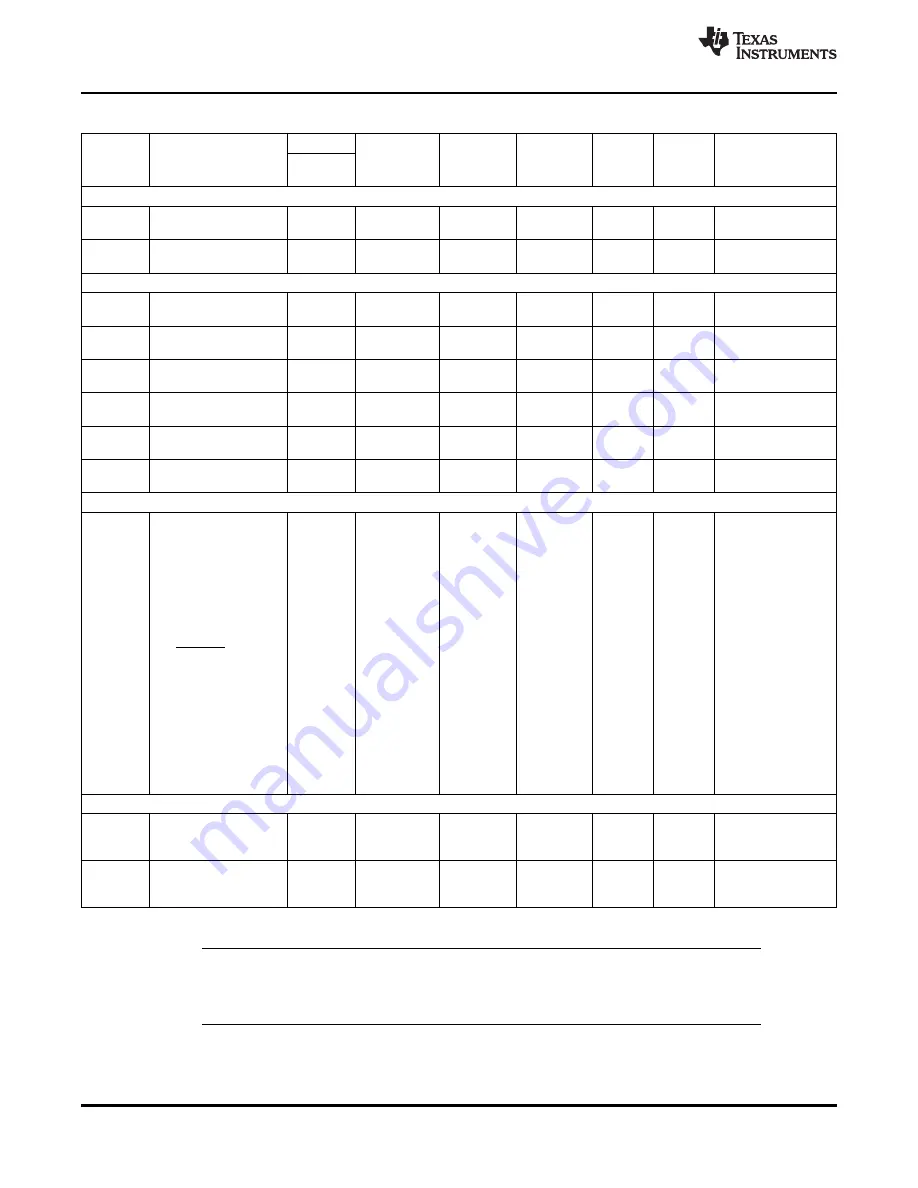

Signal Descriptions (Continued)

(1)

(continued)

PIN NO.

PERIPHERAL

DIE PAD

DIE PAD

GPIO

DIE PAD NO.

I/O/Z

(2)

PU/PD

(3)

DESCRIPTION

172-PIN

SIGNAL

X-CENTER

Y-CENTER

HFG

GPIOF OR CAN SIGNALS

GPIO or eCAN

GPIOF6

CANTXA (O)

85

99

5361.5

4758.0

I/O/Z

PU

transmit data

GPIO or eCAN

GPIOF7

CANRXA (I)

87

101

5192.7

5057.5

I/O/Z

PU

receive data

GPIOF OR McBSP SIGNALS

GPIO or transmit

GPIOF8

MCLKXA (I/O)

27

34

3461.4

42.6

I/O/Z

PU

clock

GPIO or receive

GPIOF9

MCLKRA (I/O)

24

31

3146.8

42.6

I/O/Z

PU

clock

GPIO or transmit

GPIOF10

MFSXA (I/O)

25

32

3242.2

42.6

I/O/Z

PU

frame synch

GPIO or receive

GPIOF11

MFSRA (I/O)

28

35

3556.7

42.6

I/O/Z

PU

frame synch

GPIO or transmitted

GPIOF12

MDXA (O)

21

28

2832.3

42.6

I/O/Z

–

serial data

GPIO or received

GPIOF13

MDRA (I)

19

26

2613.0

42.6

I/O/Z

PU

serial data

GPIOF OR XF CPU OUTPUT SIGNAL

This pin has three

functions:

1. XF

–

General-purpose

output pin.

2. XPLLDIS

–

This

pin is sampled

during reset to check

if the PLL needs to

GPIOF14

XF_XPLLDIS (O)

137

153

42.6

4153.3

I/O/Z

PU

be disabled. The

PLL will be disabled

if this pin is sensed

low. HALT and

STANDBY modes

cannot be used

when the PLL is

disabled.

3. GPIO

–

GPIO

function

GPIOG OR SCI-B SIGNALS

GPIO or SCI

GPIOG4

SCITXDB (O)

88

102

5098.0

5057.5

I/O/Z

–

asynchronous serial

port transmit data

GPIO or SCI

GPIOG5

SCIRXDB (I)

89

103

5003.3

5057.5

I/O/Z

–

asynchronous serial

port receive data

xxx

NOTE

Other than the power supply pins, no pin should be driven before the 3.3-V rail has reached

recommended operating conditions.

24

Introduction

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......