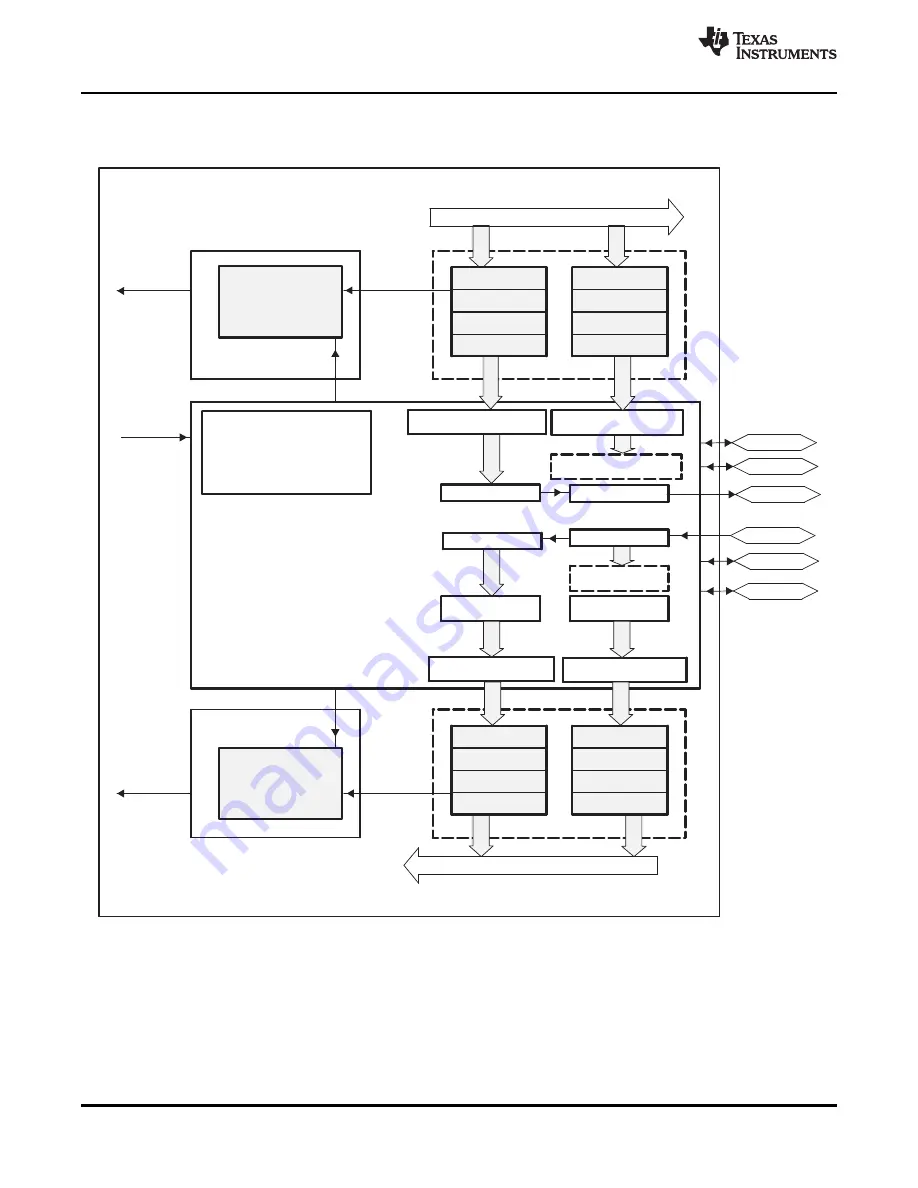

McBSP Receive

Interrupt Select Logic

DX

DR

Expand Logic

DRR1 Receive Buffer

RX FIFO

Interrupt

DRR2 Receive Buffer

RX FIFO Registers

RBR1 Register

RBR2 Register

McBSP Registers

and Control Logic

CLKX

FSX

CLKR

FSR

16

Compand Logic

DXR2 Transmit Buffer

RSR1

XSR2

XSR1

Peripheral Read Bus

16

16

16

16

16

RSR2

DXR1 Transmit Buffer

16

LSPCLK

MRINT

To CPU

McBSP

RX Interrupt Logic

RX FIFO _15

—

RX FIFO _1

RX FIFO _0

RX FIFO _15

—

RX FIFO _1

RX FIFO _0

McBSP Transmit

Interrupt Select Logic

TX FIFO

Interrupt

TX FIFO Registers

MXINT

To CPU

TX Interrupt Logic

16

16

16

TX FIFO _15

—

TX FIFO _1

TX FIFO _0

TX FIFO _15

—

TX FIFO _1

TX FIFO _0

Peripheral Write Bus

SM320F2812-HT

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

www.ti.com

Figure 4-9

shows the block diagram of the McBSP module with FIFO, interfaced to the F2812 version of

Peripheral Frame 2.

Figure 4-9. McBSP Module With FIFO

68

Peripherals

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......