10Base-T PHY Registers

A-47

Register Definitions

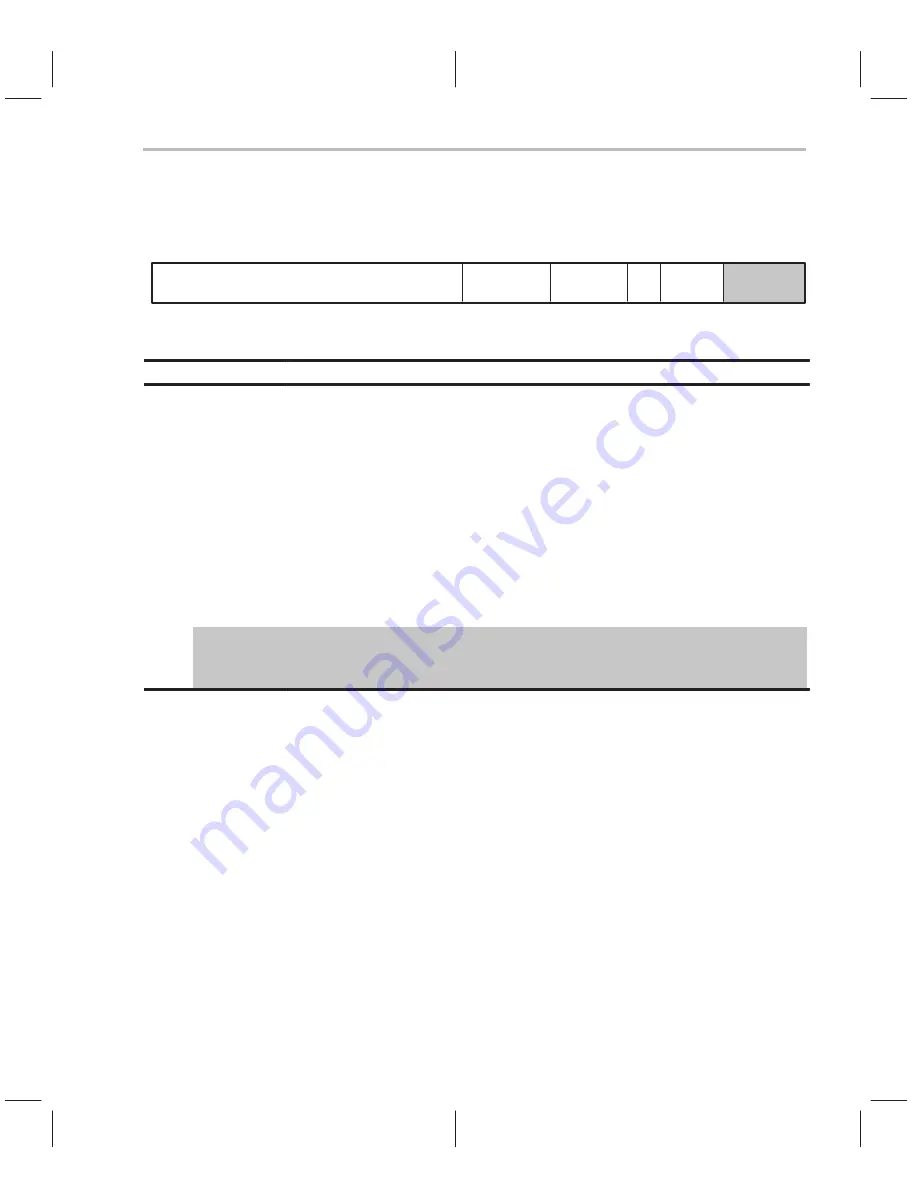

A.4.6 Autonegotiation Expansion Register – AN_exp @ 0x6

LPANABLE

PAGERX

0

LPNPABLE

PARDETFLT

Reserved

Byte 0

Byte 1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Table A–23. Autonegotiation Expansion Register Bits

Bit

Name

Function

15 – 5

Reserved

Read as 0

4

PARDETFLT

Parallel detection fault: For multi-technology PHYs, this bit indicates multiple valid links.

This PHY only supports a single technology (10Base-T) and so this bit should be

ignored.

3

LPNPABLE

Link partner next page able: When this bit is set to 1, the link partner indicates that it

implements autonegotiation next page abilities.

2

0

Next page able: ThunderLAN does not support next page transmission or reception.

1

PAGERX

Page received: This bit is set after three identical and consecutive link code words have

been received from the link partner and the link partner has indicated that it has received

three identical and consecutive link code words from ThunderLAN. This bit is cleared

when read.

0

LPANABLE

Link-Partner Autonegotiation Able: When this bit is set to a one, the PHY is receiving

autonegotiation fast link pulse bursts from the link partner. This bit is reset to zero if the

Link-Partner is not autonegotiation able.

Summary of Contents for ThunderLAN TNETE100A

Page 2: ...Printed in U S A October 1996 L411001 9761 revisionA SPWU013A ...

Page 3: ......

Page 17: ...xiv ...

Page 23: ...1 6 ...

Page 67: ...3 10 ...

Page 81: ...4 14 ...

Page 113: ...7 10 ...

Page 165: ...A 52 ...

Page 179: ...C 2 ...