TNETE211 Register Descriptions

B-7

TNETE211 100VG-AnyLAN Demand Priority Physical Media Independent (PMI) Interface

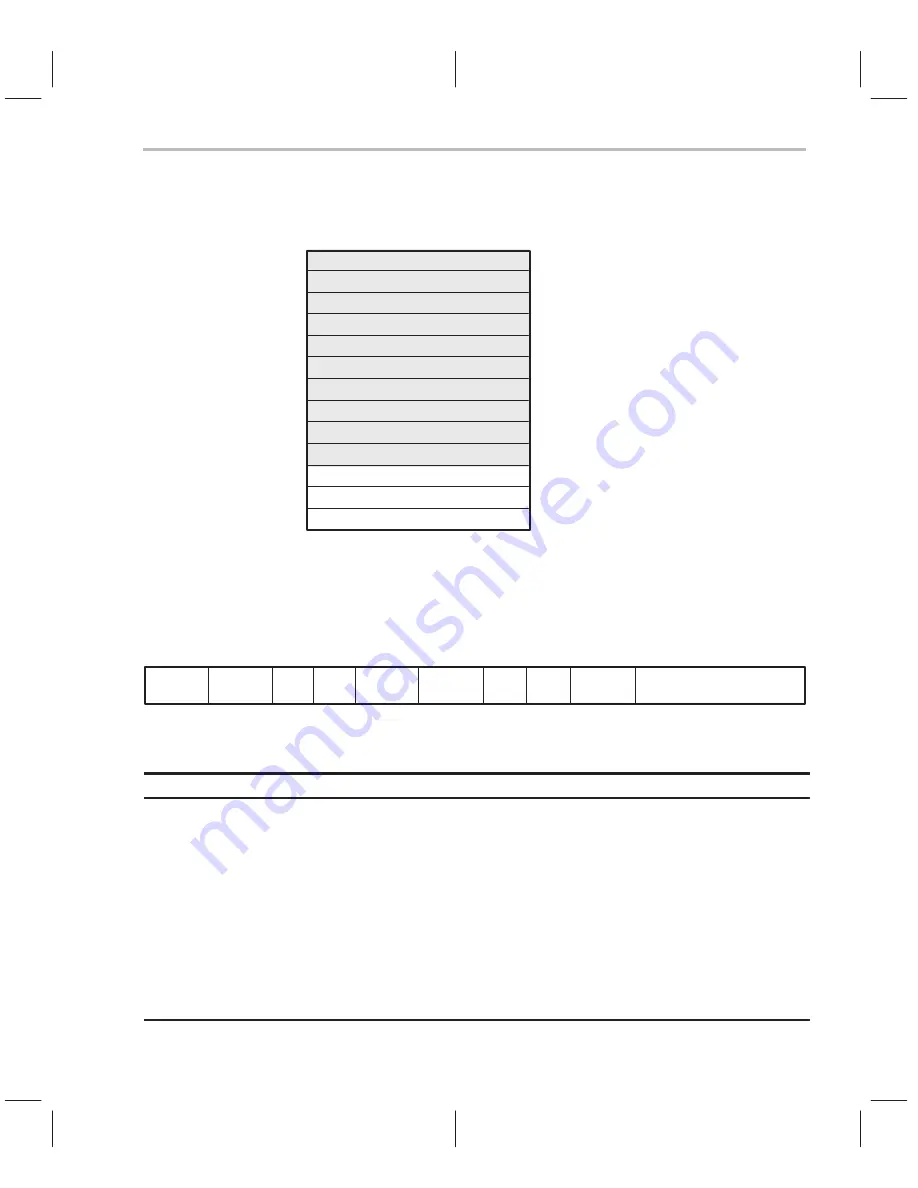

Figure B–3. TNETE211 Registers

TLPHY_sts

TLPHY_ctl

TLPHY_id

GEN_id_lo

GEN_id_hi

GEN_sts

GEN_ctl

Reserved

Reserved

Reserved

AN reserved

AN far end ability

AN advertisement

Not implemented

Not implemented

ThunderLAN PHY status register

ThunderLAN PHY identifier

Register

ThunderLAN PHY control register

Reserved by 802.3

Not implemented

PHY generic identifier (low)

PHY generic identifier (high)

PHY generic status register

PHY generic control register

0x12

0x11

0x10

0x0F

through

0x07

0x06

0x05

0x04

0x03

0x02

0x01

0x00

Description

B.2.1 PHY Generic Control Register – GEN_ctl @ 0x0

Byte 0

Byte 1

Reserved

COL

TEST

ISOLATE

PDOWN

0

LOOPBK

RESET

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

Table B–1. PHY Generic Control Register Bits

Bit

Name

Function

15

RESET

PHY reset:

Writing a 1 to this bit causes the PHY and its internal registers to reset. This

bit is self-clearing; the bit returns a value of 1 when read until the internal reset is com-

plete. This bit also serves to reset the 802.12 MAC state machine to MAC0.

14

LOOPBK

Loopback: This bit enables/disables internal loopback within the PHY device. When this

bit is set to 1 (default), data is internally wrapped within the PHY and does not appear on

the network. When this bit is set to 0, data is transmitted to and received from the network.

While the PHY is in the loopback state, all network lines are placed in a noncontentious

state. This bit also resets the 802.12 MAC state machine to MAC0.

13

0

Speed selection bit: Not implemented

12

0

Autoconfiguration enable: Not implemented

Summary of Contents for ThunderLAN TNETE100A

Page 2: ...Printed in U S A October 1996 L411001 9761 revisionA SPWU013A ...

Page 3: ......

Page 17: ...xiv ...

Page 23: ...1 6 ...

Page 67: ...3 10 ...

Page 81: ...4 14 ...

Page 113: ...7 10 ...

Page 165: ...A 52 ...

Page 179: ...C 2 ...