Test Results

53

JAJU324B – March 2015 – Revised July 2017

翻訳版

—

最新の英語版資料

http://www-s.ti.com/sc/techlit/TIDU832

Copyright © 2015–2017, Texas Instruments Incorporated

EMI/EMC

規格準拠、産業用温度範囲のデュアルポート・ギガビット・イーサネットの

リファレンス・デザイン

図

図

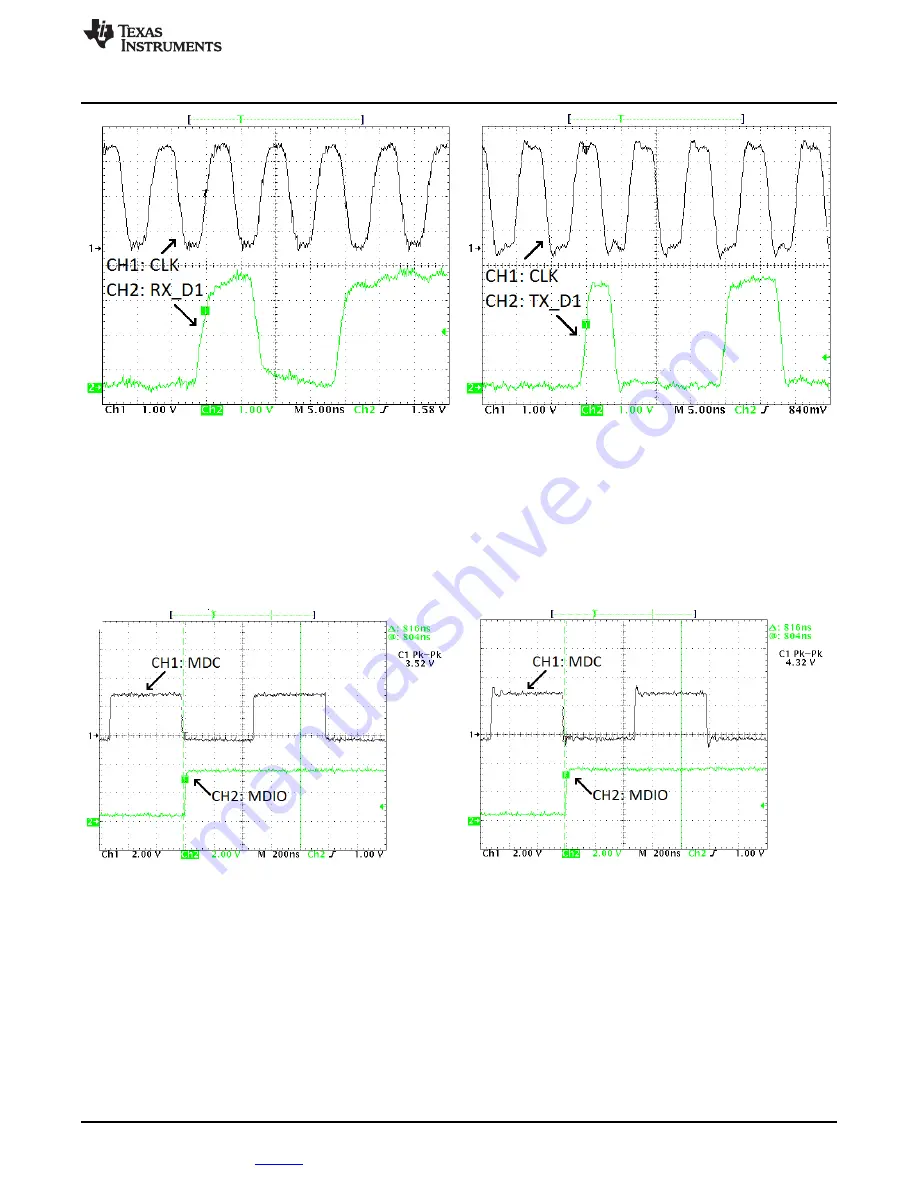

41. ETH2 RGMII RX Clock and Data Signal During

Gigabit Ethernet Connection

図

図

42. ETH2 RGMII TX Clock and Data Signal During

Gigabit Ethernet Connection

5.1.2

Serial Management Interface (SMI)

The maximum clock frequency of the SMI of the Sitara AM3359 is 2.5 MHz. This test does not need to

have an Ethernet connection running.

and

show the two signals MDC (Clock) and MDIO (I/O)

between the Sitara AM3359 and the two DP83867IR for Gigabit Ethernet ETH1 and ETH2.

図

図

43. SMI Clock and Data Signal at 2.5 MHz at

DP83867IR ETH1

図

図

44. SMI Clock and Data Signal at 2.5 MHz at

DP83867IR ETH2