1

2

3

4

5

1

0

1

1

1

1

0

0

0

0

CLK

OE(ED2)

LE(ED1)

1

2

3

0

4

6

7

5

0

1

off

on

off

on

off

on

off

on

off

on

Don't care

CLK

OE(ED2)

LE(ED1)

SDI

OUT0

OUT1

OUT2

OUT3

OUT7

SDO

SLVS695D – JUNE 2007 – REVISED JANUARY 2015

Device Functional Modes (continued)

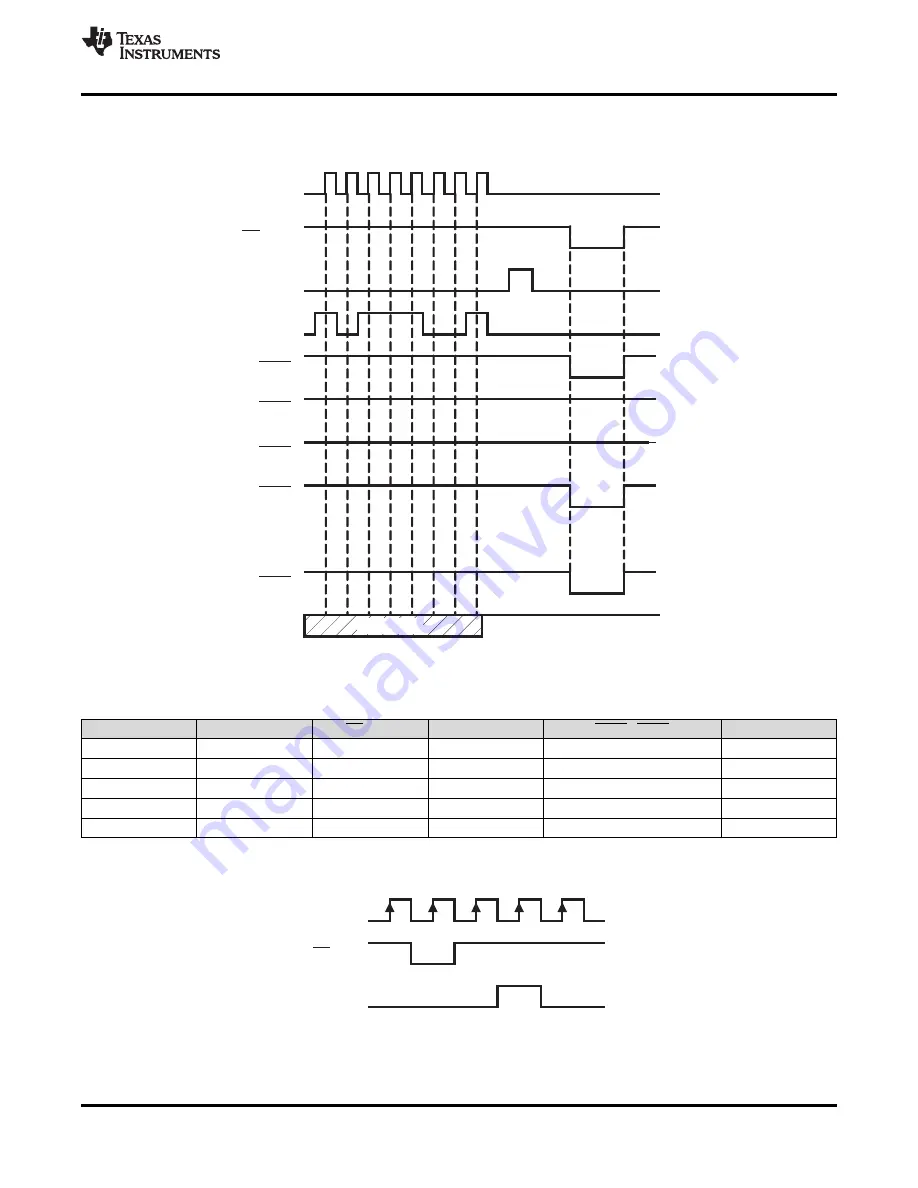

Figure 11. Normal Mode

Table 4. Truth Table in Normal Mode

CLK

LE(ED1)

OE(ED2)

SDI

OUT0...OUT7

SDO

↑

H

L

Dn

Dn...Dn – 7

Dn – 7

↑

L

L

Dn + 1

No change

Dn – 6

↑

H

L

Dn + 2

Dn + 2...Dn – 5

Dn – 5

↓

X

L

Dn + 3

Dn + 2...Dn – 5

Dn – 5

↓

X

H

Dn + 3

Off

Dn – 5

The signal sequence shown in

makes the TLC591x enter Current Adjust and Error Detection Mode.

Figure 12. Switching to Special Mode

In the Current Adjust Mode, sending the positive pulse of LE(ED1), the content of the shift register (a current

adjust code) is written to the 8-bit configuration latch (see

).

Copyright © 2007–2015, Texas Instruments Incorporated

17

Product Folder Links: