Software Interrupt

INTR

7-71

Assembly Language Instructions

Syntax

INTR

K

Operands

K:

Value from 0 to 31 that indicates the interrupt vector location

to branch to

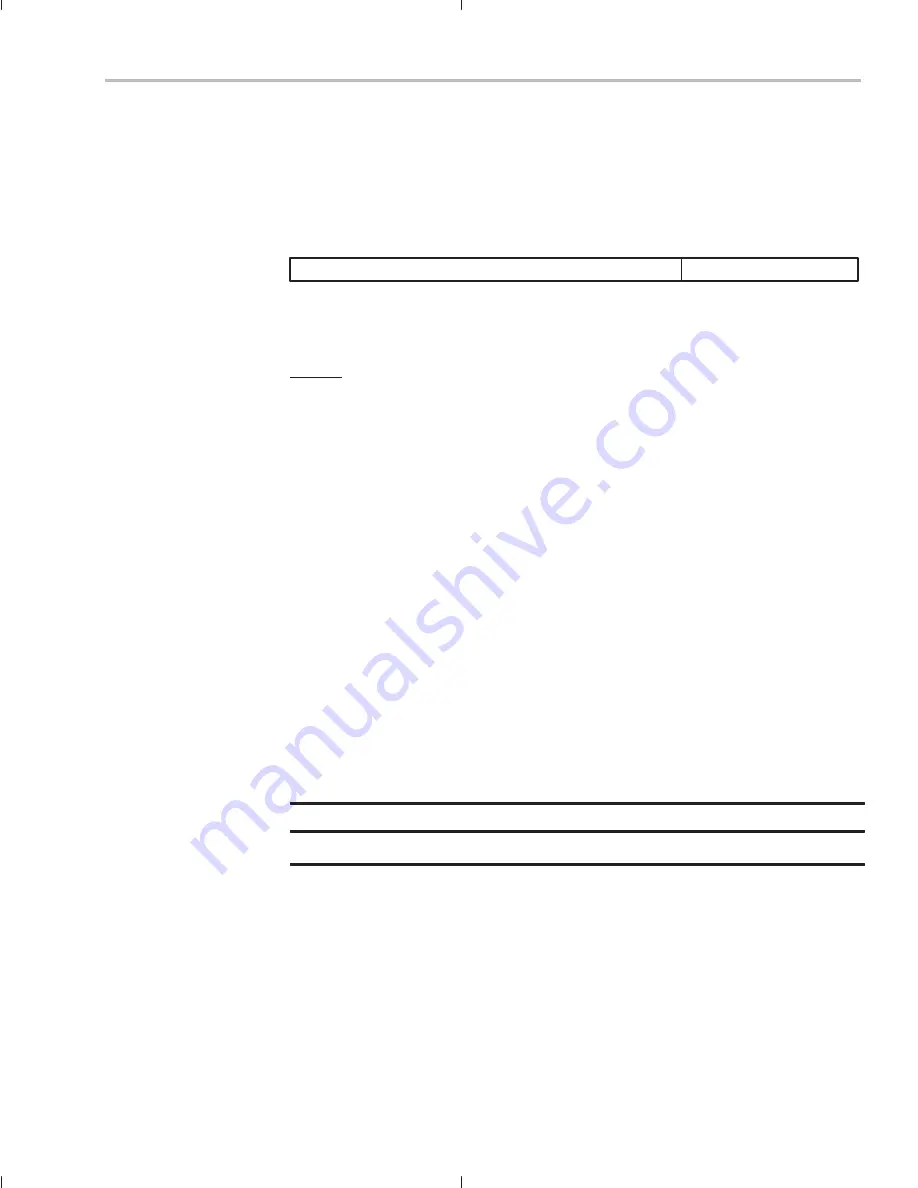

Opcode

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

K

1

1

0

0

1

1

1

1

1

0

1

Execution

(PC) + 1

→

stack

corresponding

interrupt vector location

→

PC

Status Bits

Affects

INTM

This instruction is not affected by INTM.

Description

The processor has locations for 32 interrupt vectors; each location is repre-

sented by a value K from 0 to 31. The INTR instruction is a software interrupt

that transfers program control to the program-memory address specified by

K. The vector at that address then leads to the corresponding interrupt service

routine. Thus, the instruction allows any one of the interrupt service routines

to be executed from your software. For a list of interrupts and their correspond-

ing K values, see subsection 5.6.2,

Interrupt Table, on page 5-16. During ex-

ecution of the instruction, the value PC + 1 (the return address) is pushed onto

the stack. Neither the INTM bit nor the interrupt masks affect the INTR instruc-

tion. An INTR for the external interrupts looks exactly like an external interrupt

(an interrupt acknowledge is generated, and maskable interrupts are globally

disabled by setting INTM = 1).

Words

1

Cycles for a Single INTR Instruction

ROM

DARAM

SARAM

External

4

4

4

4+3p

†

† The processor performs speculative fetching by reading two additional instruction words. If the

PC discontinuity is taken, these two instruction words are discarded.

Example

INTR

3

;PC + 1 is pushed onto the stack.

;Then control is passed to program

;memory location 6h.

Cycles