Receiver Operation

9-26

3) The remaining bits in the word are then shifted into the RSR, one by one

at the falling edge of each consecutive clock cycle.

4) After all bits have been received, if the FIFO buffer is not full, the contents

of the RSR are copied to the receive FIFO buffer. If the receive FIFO buffer

does become full, an interrupt (RINT) is sent to the CPU, and if overflow

has occurred, the overflow (OVF) bit of the SSPCR is set.

5) The process then repeats itself, except that there are no additional frame

sync pulses.

If a frame sync pulse occurs during reception, then reception is restarted and

the bits in the current word that were shifted into the RSR before the pulse are

lost.

If the FIFO buffer becomes full, no new words will be received into the buffer

until at least one word has been read from the buffer (through the SDTR). Once

the continuous reception is started, the port will always be reading in the values

on the DR pin. To stop continuous mode reception, reset the port.

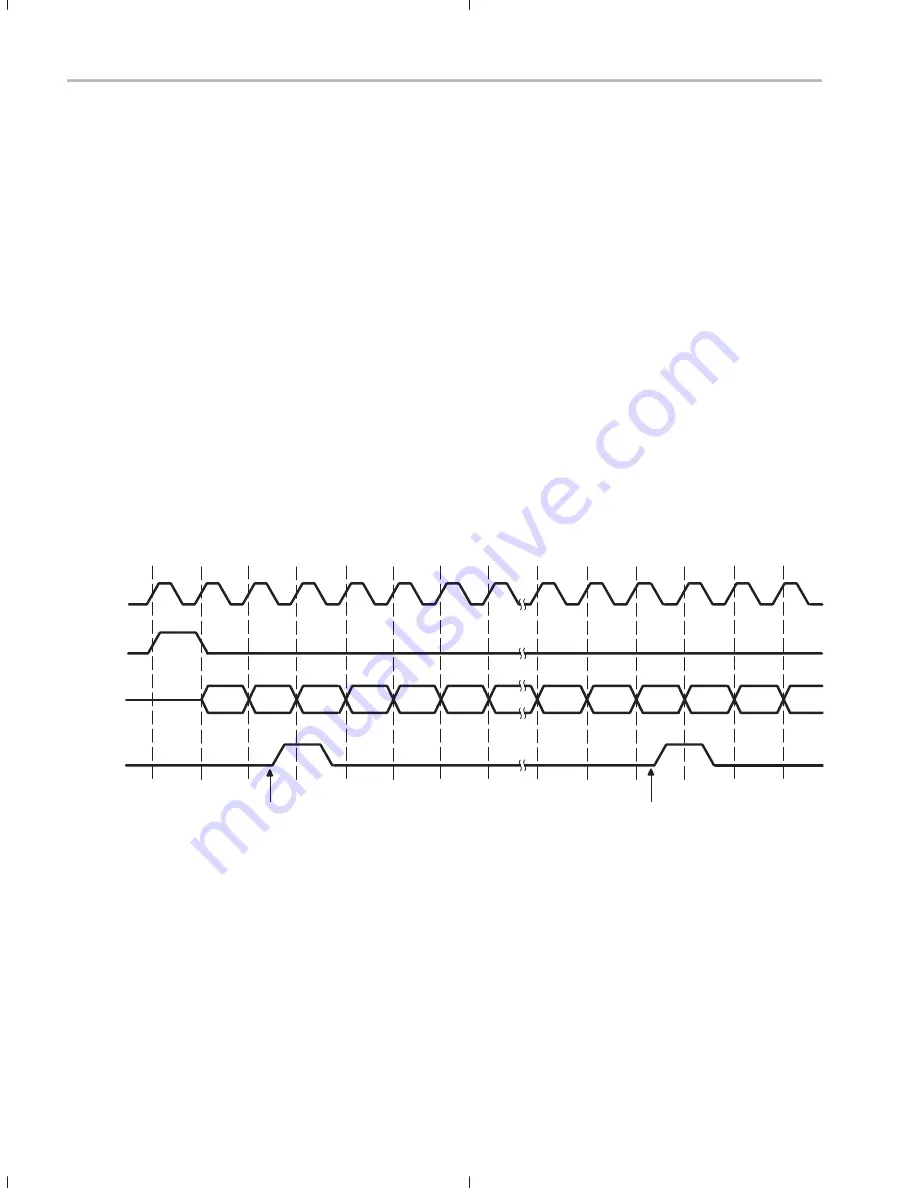

Figure 9–9. Continuous Mode Reception

CLKR

FSR

DR

RINT

Word loaded

to buffer

from RSR

A15

A14

A13

A12

A11

A10

...

A0

LSB

MSB

B15

B14

B13

B12

Word loaded

to buffer

from RSR

B11

MSB