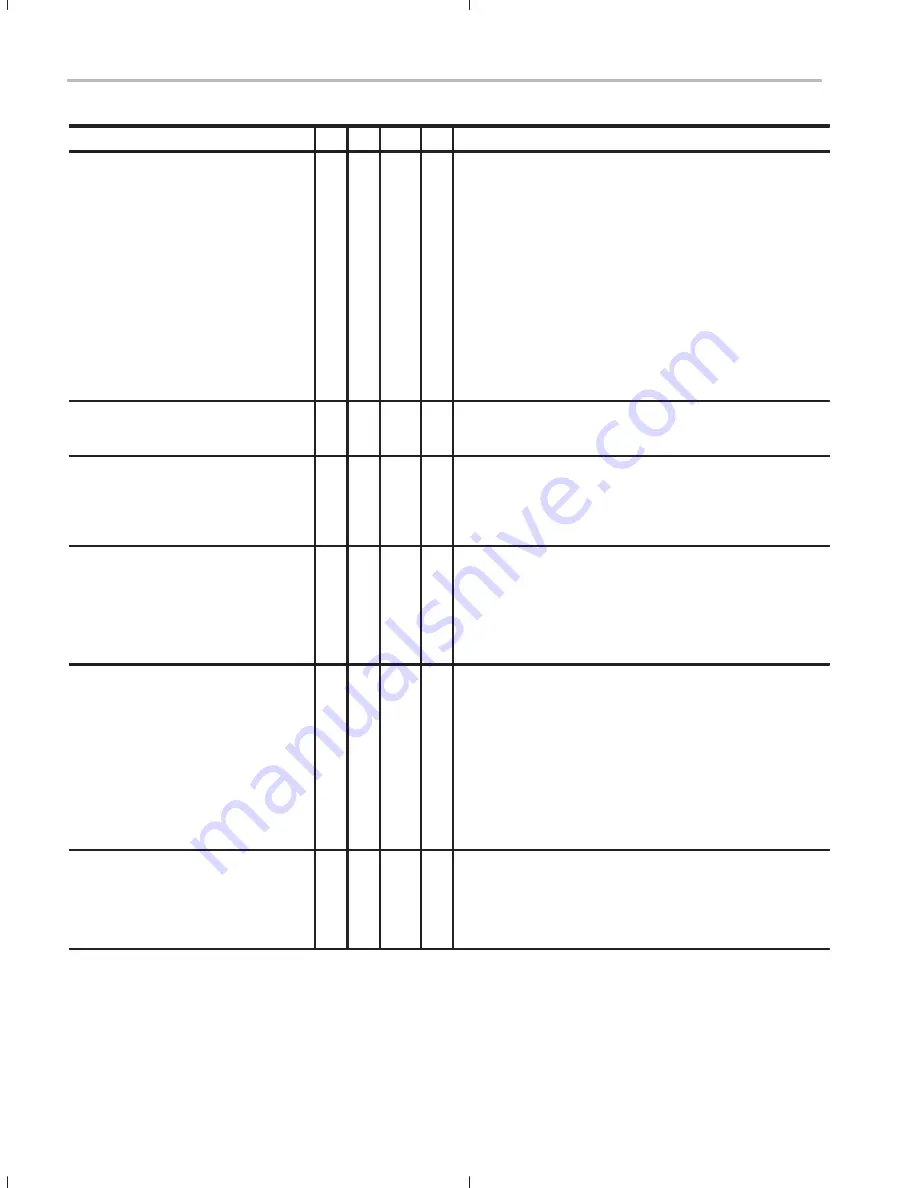

Instruction Set Comparison Table

B-8

Syntax

Description

5x

2xx

2x

1x

AND

dma

AND {

ind} [, next ARP]

AND #

lk [, shift]

√

√

√

√

√

√

√

√

√

√

AND With Accumulator

TMS320C1x and TMS320C2x devices: AND the con-

tents of the addressed data-memory location with the

16 LSBs of the accumulator. The 16 MSBs of the accu-

mulator are ANDed with 0s.

TMS320C2xx and TMS320C5x devices: AND the con-

tents of the addressed data-memory location or a

16-bit immediate value with the contents of the accu-

mulator. The 16 MSBs of the accumulator are ANDed

with 0s. If a shift is specified, left shift the constant be-

fore the AND. Low-order bits below and high-order bits

above the shifted value are treated as 0s.

ANDB

√

AND ACCB to Accumulator

AND the contents of the ACCB to the accumulator.

ANDK #

lk [, shift]

√

√

√

AND Immediate With Accumulator With Shift

AND a 16-bit immediate value with the contents of the

accumulator; if a shift is specified, left shift the constant

before the AND.

APAC

√

√

√

√

Add P Register to Accumulator

Add the contents of the P register to the accumulator.

TMS320C2x, TMS320C2xx, and TMS320C5x de-

vices: Before the add, left shift the contents of the P

register as defined by the PM status bits.

APL [#

lk] ,dma

APL [#

lk, ] {ind} [, next ARP ]

√

√

AND Data-Memory Value With DBMR or Long

Constant

AND the data-memory value with the contents of the

DBMR or a long constant. If a long constant is speci-

fied, it is ANDed with the contents of the data-memory

location. The result is written back into the data-

memory location previously holding the first operand.

If the result is 0, the TC bit is set to 1; otherwise, the TC

bit is cleared.

B

pma

B

pma [, {ind} [, next ARP ] ]

√

√

√

Branch Unconditionally

Branch to the specified program-memory address.

TMS320C2x and TMS320C2xx devices: Modify the

current AR and ARP as specified.