I/O Space

4-25

Memory and I/O Spaces

4.6.1

Accessing I/O Space

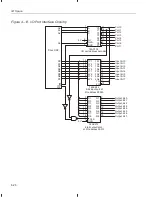

All I/O words (external I/O ports and on-chip I/O registers) are accessed with

the IN and OUT instructions. Accesses to external parallel I/O ports are multi-

plexed over the same address and data buses for program and data-memory

accesses. These accesses are distinguished from external program and data-

memory accesses by IS going low. The data bus is 16 bits wide; however, if

you use 8-bit peripherals, you can use either the higher or lower eight lines of

the data bus to suit a particular application.

You can use RD with chip-select logic to generate an output-enable signal for

an external peripheral. You can also use the WE signal with chip-select logic

to generate a write-enable signal for an external peripheral. As an example of

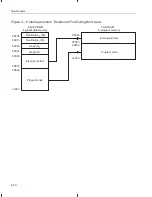

interfacing to external I/O space, Figure 4–13 shows interface circuitry for

eight input bits and eight output bits. Note that the decode section is simplified

if fewer I/O ports are used.