TMS320C6474

www.ti.com

SPRS552F – OCTOBER 2008 – REVISED JULY 2010

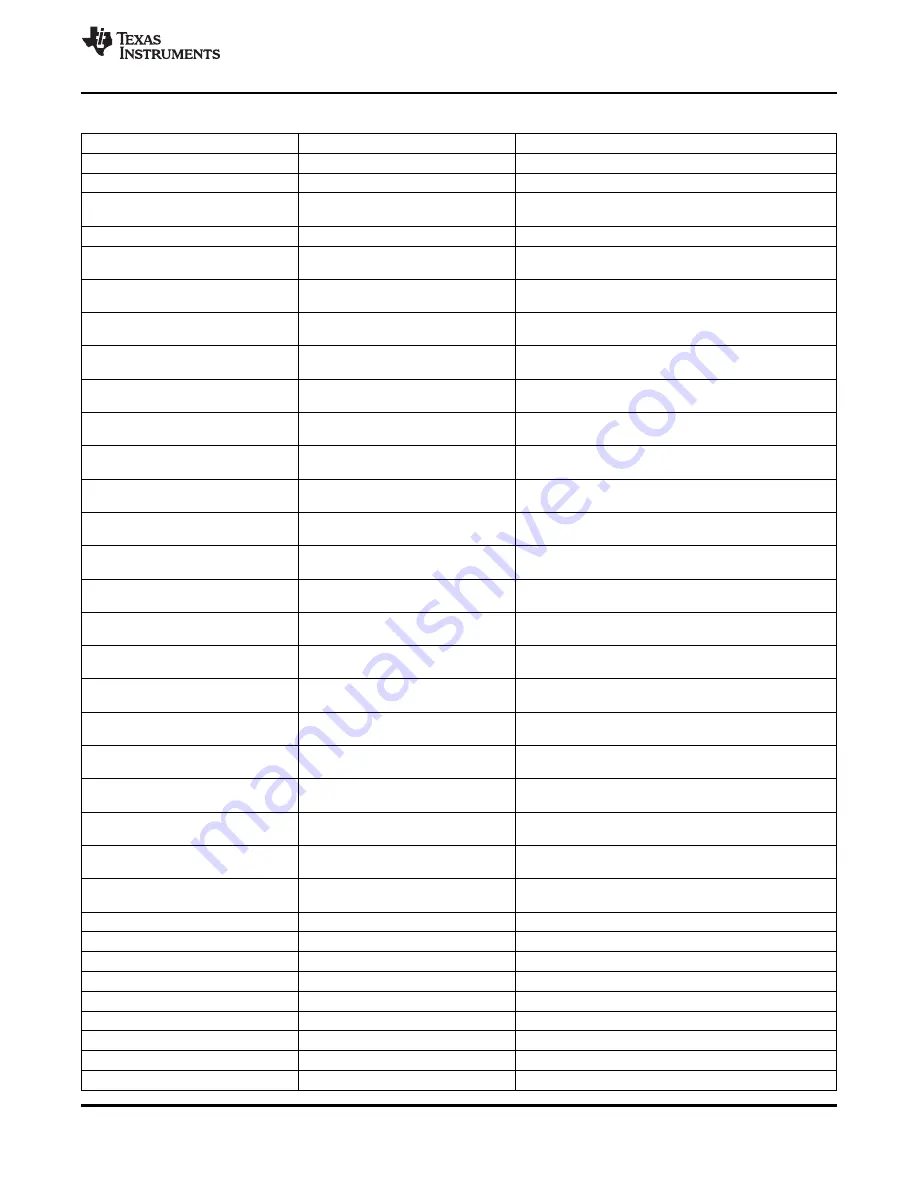

Table 7-79. RapidIO Control Registers (continued)

HEX ADDRESS

ACRONYM

REGISTER NAME

02D0 0474

RIO_LSU4_Reg5

RapidIO LSU4 Control Reg5 Register

02D0 0478

RIO_LSU4_Reg6

RapidIO LSU4 Control Reg6 Register

02D0 047C

RIO_LSU4_FLOW_MASKS

RapidIO Core3 LSU Congestion Control Flow Mask

Register

02D0 0480 - 02D0 04FC

-

Reserved

02D0 0500

RIO_Queue0_TxDMA_HDP

RapidIO Queue0 TX DMA Head Descriptor Pointer

Register

02D0 0504

RIO_Queue1_TxDMA_HDP

RapidIO Queue1 TX DMA Head Descriptor Pointer

Register

02D0 0508

RIO_Queue2_TxDMA_HDP

RapidIO Queue2 TX DMA Head Descriptor Pointer

Register

02D0 050C

RIO_Queue3_TxDMA_HDP

RapidIO Queue3 TX DMA Head Descriptor Pointer

Register

02D0 0510

RIO_Queue4_TxDMA_HDP

RapidIO Queue4 TX DMA Head Descriptor Pointer

Register

02D0 0514

RIO_Queue5_TxDMA_HDP

RapidIO Queue5 TX DMA Head Descriptor Pointer

Register

02D0 0518

RIO_Queue6_TxDMA_HDP

RapidIO Queue6 TX DMA Head Descriptor Pointer

Register

02D0 051C

RIO_Queue7_TxDMA_HDP

RapidIO Queue7 TX DMA Head Descriptor Pointer

Register

02D0 0520

RIO_Queue8_TxDMA_HDP

RapidIO Queue8 TX DMA Head Descriptor Pointer

Register

02D0 0524

RIO_Queue9_TxDMA_HDP

RapidIO Queue9 TX DMA Head Descriptor Pointer

Register

02D0 0528

RIO_Queue10_TxDMA_HDP

RapidIO Queue10 TX DMA Head Descriptor Pointer

Register

02D0 052C

RIO_Queue11_TxDMA_HDP

RapidIO Queue11TX DMA Head Descriptor Pointer

Register

02D0 0530

RIO_Queue12_TxDMA_HDP

RapidIO Queue12 TX DMA Head Descriptor Pointer

Register

02D0 0534

RIO_Queue13_TxDMA_HDP

RapidIO Queue13 TX DMA Head Descriptor Pointer

Register

02D0 0538

RIO_Queue14_TxDMA_HDP

RapidIO Queue14 TX DMA Head Descriptor Pointer

Register

02D0 053C

RIO_Queue15_TxDMA_HDP

RapidIO Queue15 TX DMA Head Descriptor Pointer

Register

02D0 0540

RIO_Queue16_TxDMA_HDP

RapidIO Queue16 TX DMA Head Descriptor Pointer

Register

02D0 0544

RIO_Queue17_TxDMA_HDP

RapidIO Queue17 TX DMA Head Descriptor Pointer

Register

02D0 0548

RIO_Queue18_TxDMA_HDP

RapidIO Queue18 TX DMA Head Descriptor Pointer

Register

02D0 054C

RIO_Queue19_TxDMA_HDP

RapidIO Queue19 TX DMA Head Descriptor Pointer

Register

02D0 0550 - 02D0 057C

-

Reserved

02D0 0580

RIO_Queue0_TxDMA_CP

RapidIO Queue0 TX DMA Completion Pointer Register

02D0 0584

RIO_Queue1_TxDMA_CP

RapidIO Queue1 TX DMA Completion Pointer Register

02D0 0588

RIO_Queue2_TxDMA_CP

RapidIO Queue2 TX DMA Completion Pointer Register

02D0 058C

RIO_Queue3_TxDMA_CP

RapidIO Queue3 TX DMA Completion Pointer Register

02D0 0590

RIO_Queue4_TxDMA_CP

RapidIO Queue4 TX DMA Completion Pointer Register

02D0 0594

RIO_Queue5_TxDMA_CP

RapidIO Queue5 TX DMA Completion Pointer Register

02D0 0598

RIO_Queue6_TxDMA_CP

RapidIO Queue6 TX DMA Completion Pointer Register

02D0 059C

RIO_Queue7_TxDMA_CP

RapidIO Queue7 TX DMA Completion Pointer Register

Copyright © 2008–2010, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications

175

Submit Documentation Feedback

Product Folder Link(s) :

TMS320C6474

Summary of Contents for TMS320C6474

Page 209: ...PACKAGE OPTION ADDENDUM www ti com 25 Sep 2010 Addendum Page 2 ...

Page 210: ......

Page 211: ......

Page 212: ......