www.ti.com

2.4 Internal Program/Data ROM and RAM

00

20

27

07

2F

28

08

0F

3F

38

37

30

1F

18

10

17

3F

38

37

30

1F

18

17

10

2F

28

27

20

0F

08

00

07

Byte

ROM Page 1

Base Address

0x0004 0000

ROM Page 0

Base Address

0x0000 0000

Bank

0

Bank

1

Bank

2

Bank

3

13

33

10

30

17

37

14

34

1B

3B

18

38

1F

3F

1C

3C

RAM Page 0

Base Address

0x1000 0000

00

20

03

23

07

04

27

24

0B

08

2B

28

0F

0C

2F

2C

Byte

Bank

0

Bank

1

Bank

2

Bank

3

Bank

4

Bank

5

Bank

6

Bank

7

TMS320C6727, TMS320C6726, TMS320C6722

Floating-Point Digital Signal Processors

SPRS268E – MAY 2005 – REVISED JANUARY 2007

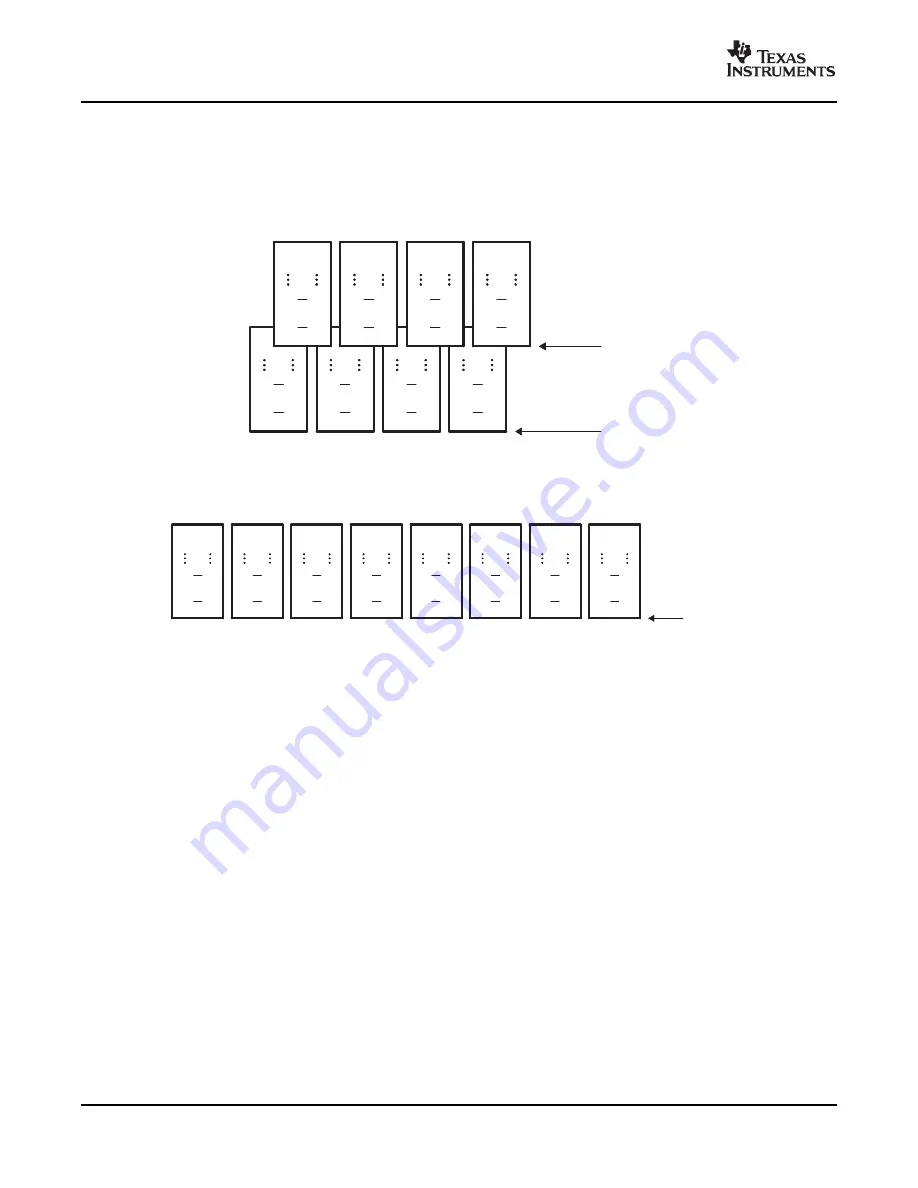

The organization of program/data ROM and RAM on C672x is simple and efficient. ROM is organized as

two 256-bit-wide pages with four 64-bit-wide banks. RAM is organized as a single 256-bit-wide page with

eight 32-bit-wide banks.

The internal memory organization is illustrated in

Figure 2-2

(ROM) and

Figure 2-3

(RAM).

Figure 2-2. Program/Data ROM Organization

Figure 2-3. Program/Data RAM Organization

The C672x memory controller supports up to three parallel accesses to the internal RAM and ROM from

three of the following four sources as long as there are no bank conflicts:

•

Two 64-bit data accesses from the C67x+ CPU

•

One 256-bit-wide program fetch from the program cache

•

One 32-bit data access from the peripheral system (either dMAX or UHPI)

A program cache miss is 256 bits wide and conflicts only with data accesses to the same page. Multiple

data accesses to different pages, or to the same page but different banks will occur without conflict.

The organization of the C672x internal memory system into multiple pages (3 total) and a large number of

banks (16 total) means that it is straightforward to optimize DSP code to avoid data conflicts. Several

factors, including the large program cache and the partitioning of the memory system into multiple pages,

minimize the number of program versus data conflicts.

The result is an efficient memory system which allows easy tuning towards the maximum possible CPU

performance.

The C672x ROM consists of a software bootloader plus additional software. Please refer to the

C9230C100 TMS320C672x Floating-Point Digital Signal Processors ROM Data Manual (literature number

SPRS277) for more details on the ROM contents.

Device Overview

10

Submit Documentation Feedback