www.ti.com

SRIO Registers

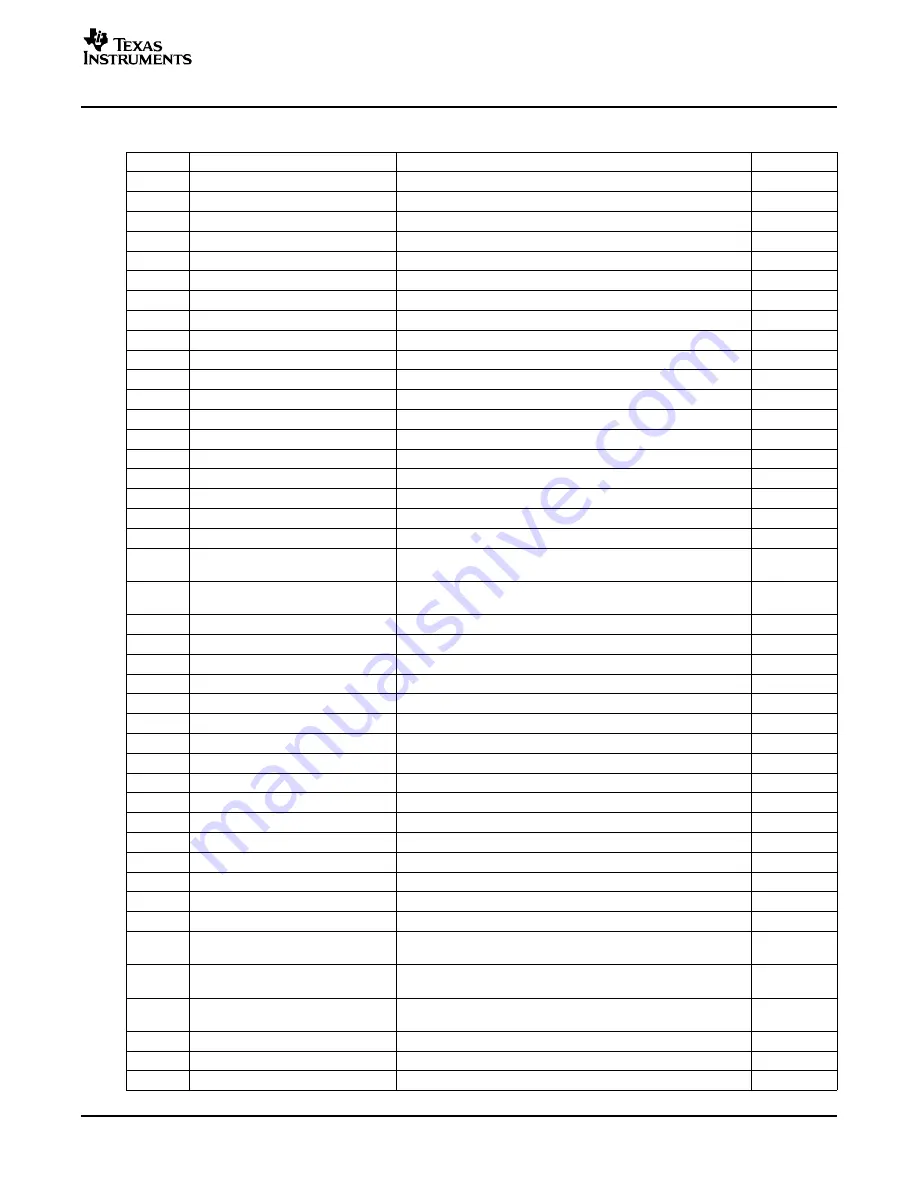

Table 40. Serial RapidIO (SRIO) Registers (continued)

Offset

Acronym

Register Description

Section

011Ch

SERDES_CFGTX3_CNTL

SERDES Transmit Channel Configuration Register 3

Section 5.14

0120h

SERDES_CFG0_CNTL

SERDES Macro Configuration Register 0

Section 5.15

0124h

SERDES_CFG1_CNTL

SERDES Macro Configuration Register 1

Section 5.15

0128h

SERDES_CFG2_CNTL

SERDES Macro Configuration Register 2

Section 5.15

012Ch

SERDES_CFG3_CNTL

SERDES Macro Configuration Register 3

Section 5.15

0200h

DOORBELL0_ICSR

DOORBELL Interrupt Condition Status Register 0

Section 5.16

0208h

DOORBELL0_ICCR

DOORBELL Interrupt Condition Clear Register 0

Section 5.17

0210h

DOORBELL1_ICSR

DOORBELL Interrupt Condition Status Register 1

Section 5.16

0218h

DOORBELL1_ICCR

DOORBELL Interrupt Condition Clear Register 1

Section 5.17

0220h

DOORBELL2_ICSR

DOORBELL Interrupt Condition Status Register 2

Section 5.16

0228h

DOORBELL2_ICCR

DOORBELL Interrupt Condition Clear Register 2

Section 5.17

0230h

DOORBELL3_ICSR

DOORBELL Interrupt Condition Status Register 3

Section 5.16

0238h

DOORBELL3_ICCR

DOORBELL Interrupt Condition Clear Register 3

Section 5.17

0240h

RX_CPPI_ICSR

RX CPPI Interrupt Condition Status Register

Section 5.18

0248h

RX_CPPI_ICCR

RX CPPI Interrupt Condition Clear Register

Section 5.19

0250h

TX_CPPI_ICSR

TX CPPI Interrupt Condition Status Register

Section 5.20

0258h

TX_CPPI_ICCR

TX CPPI Interrupt Condition Clear Register

Section 5.21

0260h

LSU_ICSR

LSU Interrupt Condition Status Register

Section 5.22

0268h

LSU_ICCR

LSU Interrupt Condition Clear Register

Section 5.23

0270h

ERR_RST_EVNT_ICSR

Error, Reset, and Special Event Interrupt Condition Status

Section 5.24

Register

0278h

ERR_RST_EVNT_ICCR

Error, Reset, and Special Event Interrupt Condition Clear

Section 5.25

Register

0280h

DOORBELL0_ICRR

DOORBELL0 Interrupt Condition Routing Register

Section 5.26

0284h

DOORBELL0_ICRR2

DOORBELL 0 Interrupt Condition Routing Register 2

Section 5.26

0290h

DOORBELL1_ICRR

DOORBELL1 Interrupt Condition Routing Register

Section 5.26

0294h

DOORBELL1_ICRR2

DOORBELL 1 Interrupt Condition Routing Register 2

Section 5.26

02A0h

DOORBELL2_ICRR

DOORBELL2 Interrupt Condition Routing Register

Section 5.26

02A4h

DOORBELL2_ICRR2

DOORBELL 2 Interrupt Condition Routing Register 2

Section 5.26

02B0h

DOORBELL3_ICRR

DOORBELL3 Interrupt Condition Routing Register

Section 5.26

02B4h

DOORBELL3_ICRR2

DOORBELL 3 Interrupt Condition Routing Register 2

Section 5.26

02C0h

RX_CPPI _ICRR

Receive CPPI Interrupt Condition Routing Register

Section 5.27

02C4h

RX_CPPI _ICRR2

Receive CPPI Interrupt Condition Routing Register 2

Section 5.27

02D0h

TX_CPPI _ICRR

Transmit CPPI Interrupt Condition Routing Register

Section 5.28

02D4h

TX_CPPI _ICRR2

Transmit CPPI Interrupt Condition Routing Register 2

Section 5.28

02E0h

LSU_ICRR0

LSU Interrupt Condition Routing Register 0

Section 5.29

02E4h

LSU_ICRR1

LSU Interrupt Condition Routing Register 1

Section 5.29

02E8h

LSU_ICRR2

LSU Interrupt Condition Routing Register 2

Section 5.29

02ECh

LSU_ICRR3

LSU Interrupt Condition Routing Register 3

Section 5.29

02F0h

ERR_RST_EVNT_ICRR

Error, Reset, and Special Event Interrupt Condition Routing

Section 5.30

Register

02F4h

ERR_RST_EVNT_ICRR2

Error, Reset, and Special Event Interrupt Condition Routing

Section 5.30

Register 2

02F8h

ERR_RST_EVNT_ICRR3

Error, Reset, and Special Event Interrupt Condition Routing

Section 5.30

Register 3

0300h

INTDST0_DECODE

INTDST Interrupt Status Decode Register 0

Section 5.31

0304h

INTDST1_DECODE

INTDST Interrupt Status Decode Register 1

Section 5.31

0308h

INTDST2_DECODE

INTDST Interrupt Status Decode Register 2

Section 5.31

SPRUE13A – September 2006

Serial RapidIO (SRIO)

103

Submit Documentation Feedback