www.ti.com

SRIO Registers

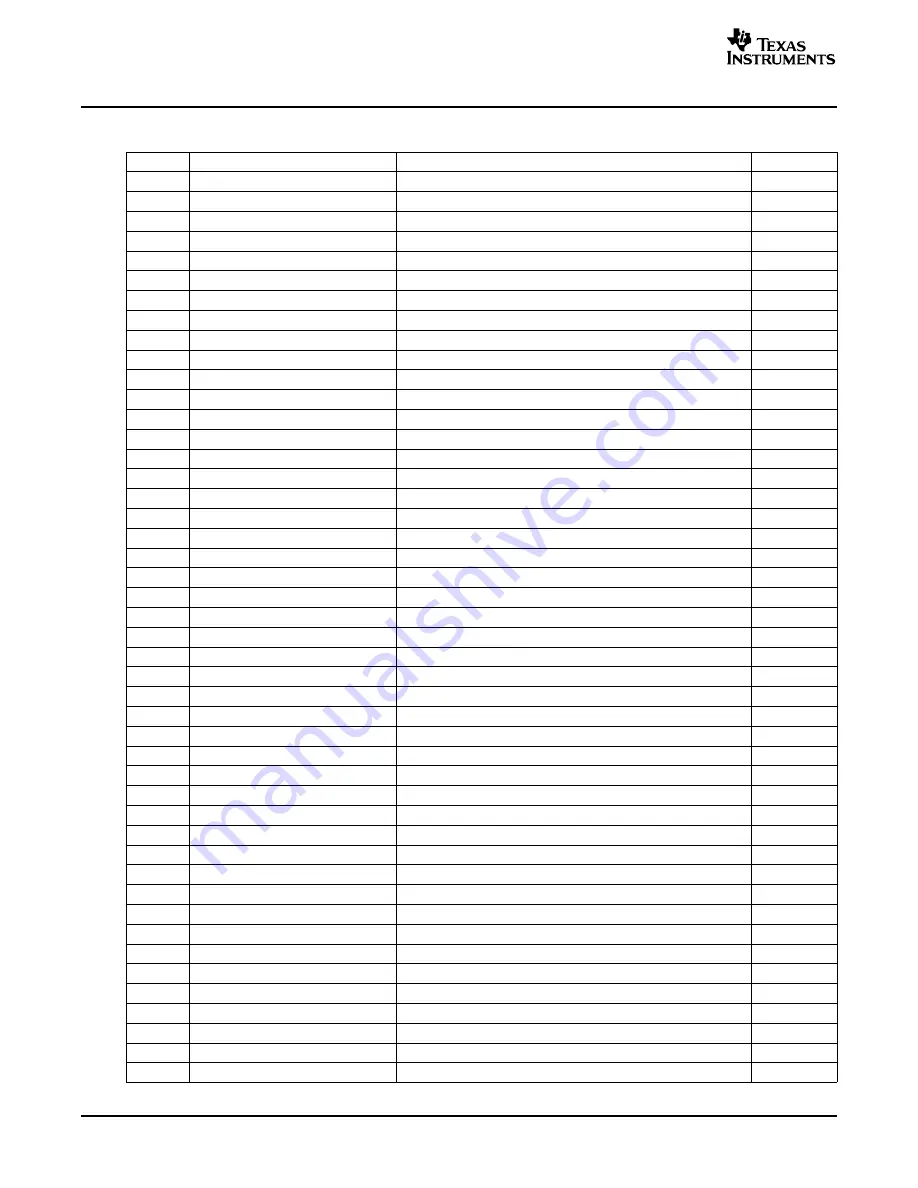

Table 40. Serial RapidIO (SRIO) Registers (continued)

Offset

Acronym

Register Description

Section

08F0h

RXU_MAP_L30

MailBox-to-Queue Mapping Register L30

Section 5.50

08F4h

RXU_MAP_H30

MailBox-to-Queue Mapping Register H30

Section 5.50

08F8h

RXU_MAP_L31

MailBox-to-Queue Mapping Register L31

Section 5.50

08FCh

RXU_MAP_H31

MailBox-to-Queue Mapping Register H31

Section 5.50

0900h

FLOW_CNTL0

Flow Control Table Entry Register 0

Section 5.51

0904h

FLOW_CNTL1

Flow Control Table Entry Register 1

Section 5.51

0908h

FLOW_CNTL2

Flow Control Table Entry Register 2

Section 5.51

090Ch

FLOW_CNTL3

Flow Control Table Entry Register 3

Section 5.51

0910h

FLOW_CNTL4

Flow Control Table Entry Register 4

Section 5.51

0914h

FLOW_CNTL5

Flow Control Table Entry Register 5

Section 5.51

0918h

FLOW_CNTL6

Flow Control Table Entry Register 6

Section 5.51

091Ch

FLOW_CNTL7

Flow Control Table Entry Register 7

Section 5.51

0920h

FLOW_CNTL8

Flow Control Table Entry Register 8

Section 5.51

0924h

FLOW_CNTL9

Flow Control Table Entry Register 9

Section 5.51

0928h

FLOW_CNTL10

Flow Control Table Entry Register 10

Section 5.51

092Ch

FLOW_CNTL11

Flow Control Table Entry Register 11

Section 5.51

0930h

FLOW_CNTL12

Flow Control Table Entry Register 12

Section 5.51

0934h

FLOW_CNTL13

Flow Control Table Entry Register 13

Section 5.51

0938h

FLOW_CNTL14

Flow Control Table Entry Register 14

Section 5.51

093Ch

FLOW_CNTL15

Flow Control Table Entry Register 15

Section 5.51

1000h

DEV_ID

Device Identity CAR

Section 5.52

1004h

DEV_INFO

Device Information CAR

Section 5.53

1008h

ASBLY_ID

Assembly Identity CAR

Section 5.54

100Ch

ASBLY_INFO

Assembly Information CAR

Section 5.55

1010h

PE_FEAT

Processing Element Features CAR

Section 5.56

1018h

SRC_OP

Source Operations CAR

Section 5.57

101Ch

DEST_OP

Destination Operations CAR

Section 5.58

104Ch

PE_LL_CTL

Processing Element Logical Layer Control CSR

Section 5.59

1058h

LCL_CFG_HBAR

Local Configuration Space Base Address 0 CSR

Section 5.60

105Ch

LCL_CFG_BAR

Local Configuration Space Base Address 1 CSR

Section 5.61

1060h

BASE_ID

Base Device ID CSR

Section 5.62

1068h

HOST_BASE_ID_LOCK

Host Base Device ID Lock CSR

Section 5.63

106Ch

COMP_TAG

Component Tag CSR

Section 5.64

1100h

SP_MB_HEAD

1x/4x LP_Serial Port Maintenance Block Header

Section 5.65

1120h

SP_LT_CTL

Port Link Time-Out Control CSR

Section 5.66

1124h

SP_RT_CTL

Port Response Time-Out Control CSR

Section 5.67

113Ch

SP_GEN_CTL

Port General Control CSR

Section 5.68

1140h

SP0_LM_REQ

Port 0 Link Maintenance Request CSR

Section 5.69

1144h

SP0_LM_RESP

Port 0 Link Maintenance Response CSR

Section 5.70

1148h

SP0_ACKID_STAT

Port 0 Local AckID Status CSR

Section 5.71

1158h

SP0_ERR_STAT

Port 0 Error and Status CSR

Section 5.72

115Ch

SP0_CTL

Port 0 Control CSR

Section 5.73

1160h

SP1_LM_REQ

Port 1 Link Maintenance Request CSR

Section 5.69

1164h

SP1_LM_RESP

Port 1 Link Maintenance Response CSR

Section 5.70

1168h

SP1_ACKID_STAT

Port 1 Local AckID Status CSR

Section 5.71

1178h

SP1_ERR_STAT

Port 1 Error and Status CSR

Section 5.72

108

Serial RapidIO (SRIO)

SPRUE13A – September 2006

Submit Documentation Feedback