www.ti.com

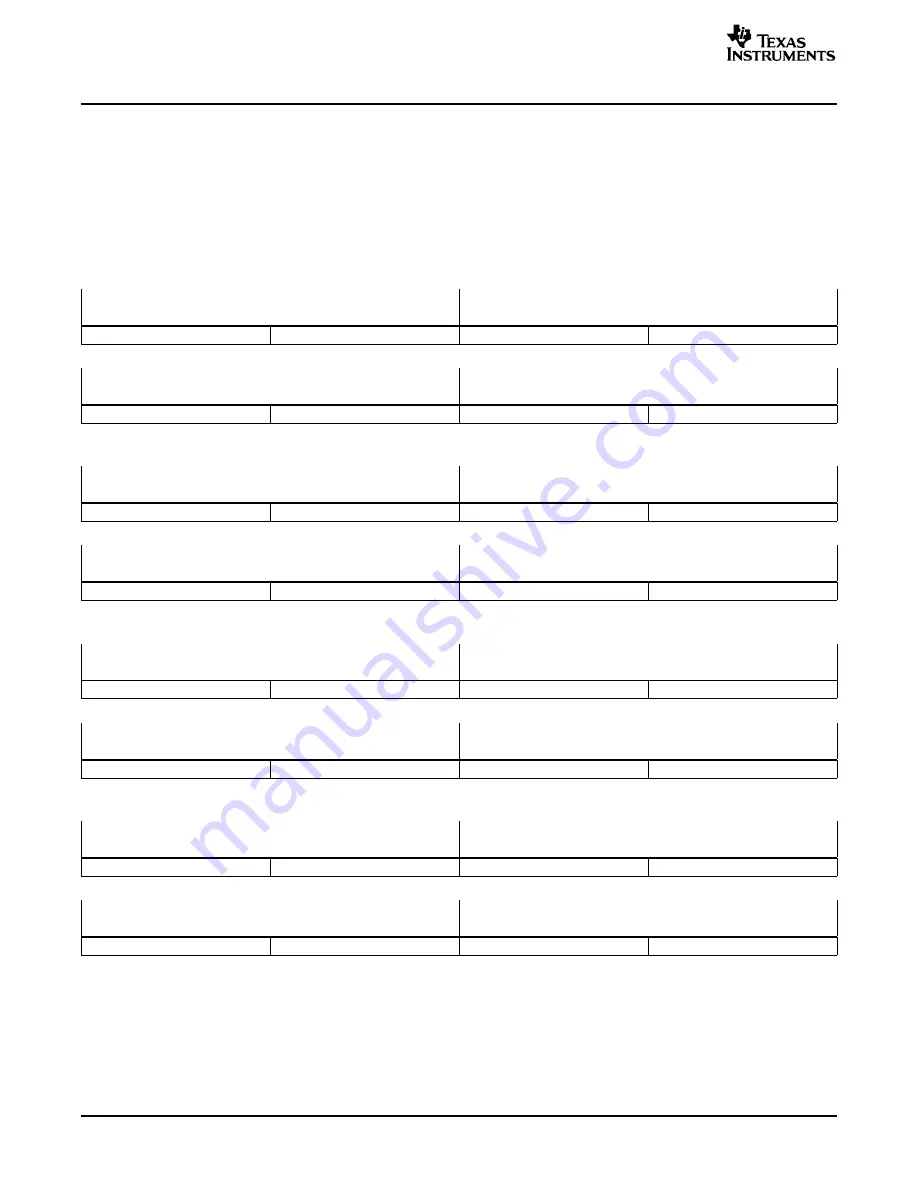

5.49 Transmit CPPI Weighted Round Robin Control Registers (TX_QUEUE_CNTL[0–3])

SRIO Registers

The transmission order among TX buffer descriptor queues is based on the programmable weighted

round-robin scheme explained in

Section 2.3.4.2

. As part of this scheme, software must program the 16

mappers to determine the order in which the queues are serviced and how many messages are handled

in each queue during each time around the round-robin cycle. The mappers are programmed with the

registers shown in

Figure 112

. The register fields are described in

Table 117

. For additional programming

information, see

Section 2.3.4.2

.

Figure 112. Transmit CPPI Weighted Round Robin Control Registers

TX_QUEUE_CNTL0 - Address Offset 07E0h

<-------------------------------- TX_Queue_Map3 ----------------------------->

<-------------------------------- TX_Queue_Map2 ----------------------------->

31

28 27

24 23

20 19

16

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-3h

R/W-0

R/W-2h

<-------------------------------- TX_Queue_Map1 ----------------------------->

<-------------------------------- TX_Queue_Map0 ----------------------------->

15

12 11

8 7

4 3

0

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-1h

R/W-0h

R/W-0h

TX_QUEUE_CNTL1 - Address Offset 07E4h

<-------------------------------- TX_Queue_Map7 ----------------------------->

<-------------------------------- TX_Queue_Map6 ----------------------------->

31

28 27

24 23

20 19

16

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0

R/W-7h

R/W-0h

R/W-6h

<-------------------------------- TX_Queue_Map5 ----------------------------->

<-------------------------------- TX_Queue_Map4 ----------------------------->

15

12 11

8 7

4 3

0

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-5h

R/W-0h

R/W-4h

TX_QUEUE_CNTL2 - Address Offset 07E8h

<-------------------------------- TX_Queue_Map11 ----------------------------->

<-------------------------------- TX_Queue_Map10 ----------------------------->

31

28 27

24 23

20 19

16

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-Bh

R/W-0h

R/W-Ah

<-------------------------------- TX_Queue_Map9 ----------------------------->

<-------------------------------- TX_Queue_Map8 ----------------------------->

15

12 11

8 7

4 3

0

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-9h

R/W-0h

R/W-8h

TX_QUEUE_CNTL3 - Address Offset 07ECh

<-------------------------------- TX_Queue_Map15 ----------------------------->

<-------------------------------- TX_Queue_Map14 ----------------------------->

31

28 27

24 23

20 19

16

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-Fh

R/W-0h

R/W-Eh

<-------------------------------- TX_Queue_Map13 ----------------------------->

<-------------------------------- TX_Queue_Map12 ----------------------------->

15

12 11

8 7

4 3

0

Number of Msgs

Queue Pointer

Number of Msgs

Queue Pointer

R/W-0h

R/W-Dh

R/W-0h

R/W-Ch

174

Serial RapidIO (SRIO)

SPRUE13A – September 2006

Submit Documentation Feedback