www.ti.com

5.60 Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR)

SRIO Registers

The local configuration space base address 0 CSR (LCL_CFG_HBAR) is shown in

Figure 123

and

described in

Table 131

.

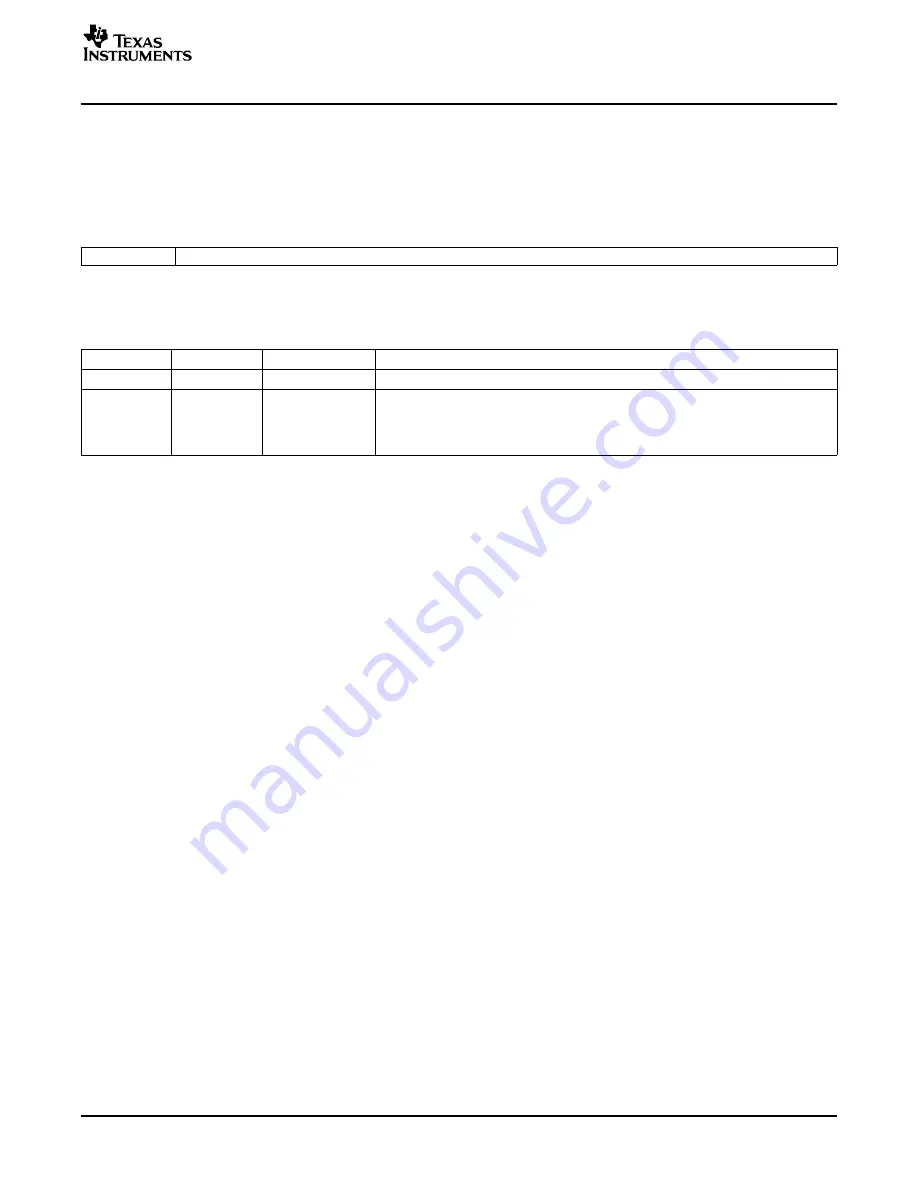

Figure 123. Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR) - Address Offset

1058h

31

30

0

Reserved

LCSBA

R-0

R-00000000h

LEGEND: R = Read only; -n = Value after reset

Table 131. Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR) Field Descriptions

Bit

Field

Value

Description

31

Reserved

0

These read-only bits return 0s when read.

30–0

LCSBA

00000000h

Bits 30 to 15 are reserved for 34-bit addresses, reserved for 50-bit addresses, and

to

bits 66 to 51 of a 66-bit address.

FFFFFFFFh

Bits 14 to 0 are reserved for 34-bit addresses, bits 50 to 36 of a 50-bit address, and

bits 50 to 36 of a 66-bit address.

SPRUE13A – September 2006

Serial RapidIO (SRIO)

191

Submit Documentation Feedback