www.ti.com

2.3.2.3

Enabling the Transmitter

SRIO Functional Description

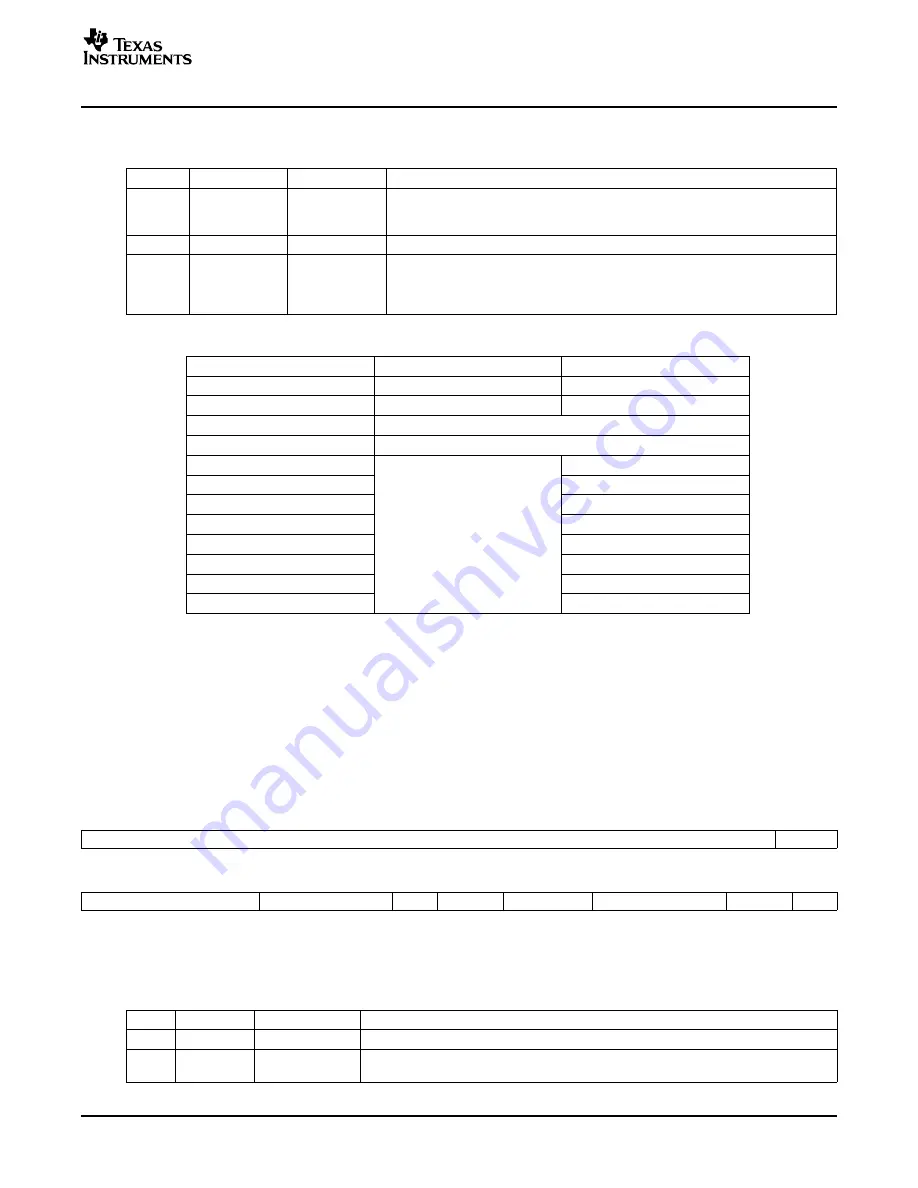

Table 9. SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL) Field

Descriptions (continued)

Bit

Field

Value

Description

4–2

BUSWIDTH

000b

Bus width. Always write 000b to this field, to indicate a 10-bit-wide parallel bus to

the clock. All other values are reserved. See

Section 2.3.2.1

for an explanation of

the bus.

1

Reserved

0

Always write 0 to this reserved bit.

0

ENRX

Enable receiver

0

Disable this receiver.

1

Enable this receiver.

Table 10. EQ Bits

CFGRX[22–19]

Low Freq Gain

Zero Freq (at e

28

(min))

0000b

Maximum

–

0001b

Adaptive

Adaptive

001xb

Reserved

01xxb

Reserved

1000b

Adaptive

1084MHz

1001b

805MHz

1010b

573MHz

1011b

402MHz

1100b

304MHz

1101b

216MHz

1110b

156MHz

1111b

135MHz

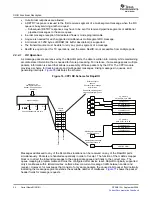

To enable a transmitter for serialization, the ENTX bit of the associated SERDES_CFGTXn_CNTL

registers (110h–10Ch) must be set high. When ENTX is low, all digital circuitry within the transmitter will

be disabled, and clocks will be gated off, with the exception of the transmit clock (TXBCLK[n]) output,

which will continue to operate normally. All current sources within the transmitter will be fully powered

down, with the exception of the current mode logic (CML) driver, which will remain powered up if boundary

scan is selected.

Figure 11

shows the fields of SERDES_CFGTXn_CNTL and

Table 11

describes them.

Figure 11. SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL)

31

17

16

Reserved

ENFTP

R-0

R/W-1

15

12 11

9

8

7

6

5 4

2

1

0

DE

SWING

CM

INVPAIR

RATE

BUSWIDTH

(write 0)

ENTX

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Table 11. SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field

Descriptions

Bit

Field

Value

Description

31–17

Reserved

0

These read-only bits return 0s when read.

16

ENFTP

1

Enables fixed phase relationship of transmit input clock with respect to transmit output

clock. The only valid value for this field is 1b; all other values are reserved.

SPRUE13A – September 2006

Serial RapidIO (SRIO)

33

Submit Documentation Feedback