www.ti.com

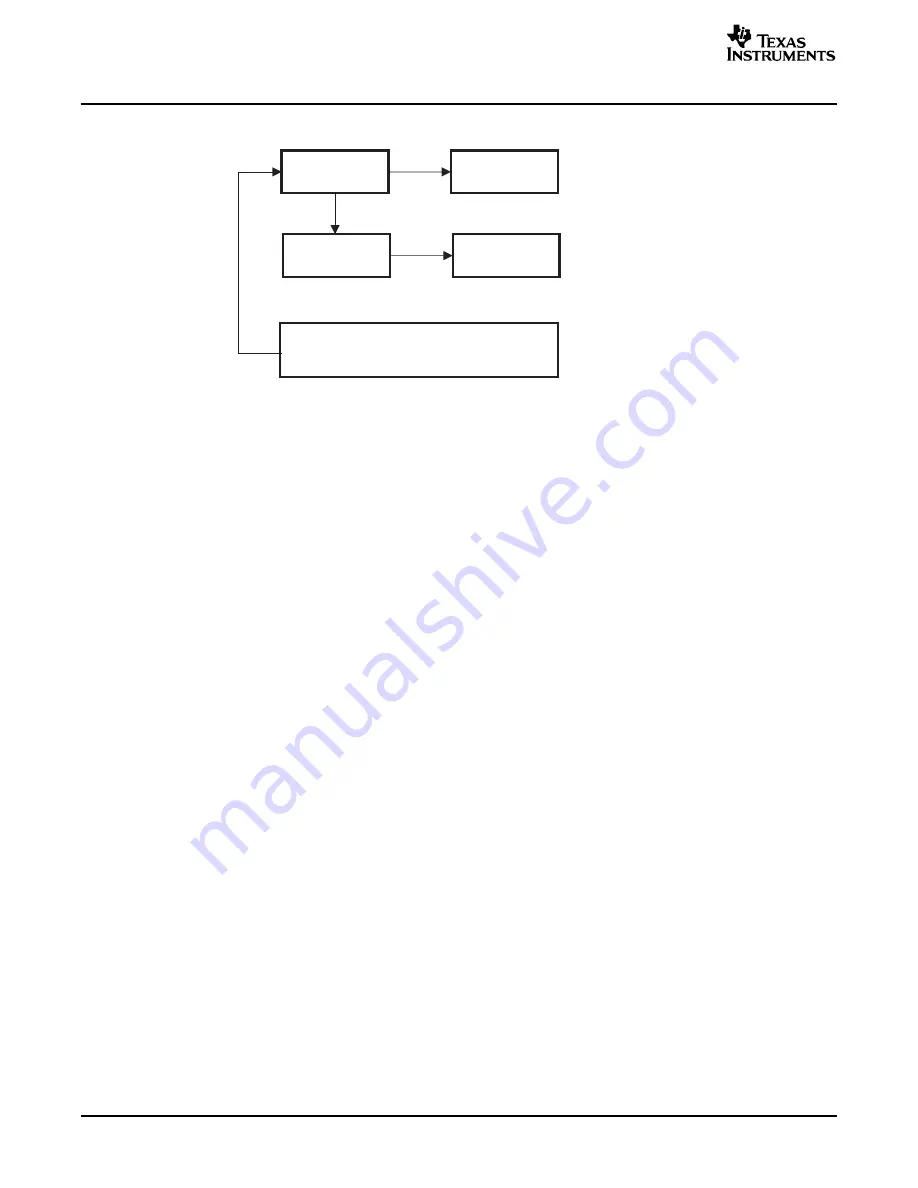

Descriptor

Descriptor

Buffer

Buffer

Port RX DMA

state

RX queue head descriptor

pointer

SRIO Functional Description

Figure 24. RX Buffer Descriptors

TX Buffer Descriptor

TX_DESCP0_0->TXDESC0 =

CSL_FMK( SRIO_TXDESC0_N_POINTER,(int )TX_DESCP0_1 );

//link to

TX_DESCP0_1

TX_DESCP0_0->TXDESC1 =

CSL_FMK( SRIO_TXDESC1_B_POINTER,(int )&xmtBuff1[0] );

//Buffer

Pointer

TX_DESCP0_0->TXDESC2 =

CSL_FMK( SRIO_TXDESC2_DESTID, 0xBEEF)

|

CSL_FMK( SRIO_TXDESC2_PRI, 1)

|

CSL_FMK( SRIO_TXDESC2_TT, 1)

|

CSL_FMK( SRIO_TXDESC2_PORTID, 3)

|

CSL_FMK( SRIO_TXDESC2_SSIZE, SSIZE_256B)|

CSL_FMK( SRIO_TXDESC2_MAILBOX, 0);

TX_DESCP0_0->TXDESC3 =

CSL_FMK( SRIO_TXDESC3_SOP,1 )

|

CSL_FMK( SRIO_TXDESC3_EOP,1 )

|

CSL_FMK( SRIO_TXDESC3_OWNERSHIP,1 )

|

CSL_FMK( SRIO_TXDESC3_EOQ,1 )

|

CSL_FMK( SRIO_TXDESC3_TEARDOWN,0 )

|

CSL_FMK( SRIO_TXDESC3_RETRY_COUNT,0 )|

CSL_FMK( SRIO_TXDESC3_MESSAGE_LENGTH,MLEN_512DW );

TX_DESCP0_1->TXDESC0 =

CSL_FMK( SRIO_TXDESC0_N_POINTER, 0);

//end of message

TX_DESCP0_1->TXDESC1 =

CSL_FMK( SRIO_TXDESC1_B_POINTER,(int )&xmtBuff2[0] );

TX_DESCP0_1->TXDESC2 =

CSL_FMK( SRIO_TXDESC2_DESTID, 0xBEEF)

|

CSL_FMK( SRIO_TXDESC2_PRI, 1)

|

CSL_FMK( SRIO_TXDESC2_TT, 1)

|

CSL_FMK( SRIO_TXDESC2_PORTID, 3)

|

CSL_FMK( SRIO_TXDESC2_SSIZE, SSIZE_256B)|

CSL_FMK( SRIO_TXDESC2_MAILBOX, 1);

TX_DESCP0_1->TXDESC3 =

CSL_FMK( SRIO_TXDESC3_SOP,1 )

|

CSL_FMK( SRIO_TXDESC3_EOP,1 )

|

CSL_FMK( SRIO_TXDESC3_OWNERSHIP,1 )

|

CSL_FMK( SRIO_TXDESC3_EOQ,1 )

|

CSL_FMK( SRIO_TXDESC3_TEARDOWN,0 )

|

CSL_FMK( SRIO_TXDESC3_RETRY_COUNT,0 )|

CSL_FMK( SRIO_TXDESC3_MESSAGE_LENGTH,MLEN_512DW );

62

Serial RapidIO (SRIO)

SPRUE13A – September 2006

Submit Documentation Feedback