www.ti.com

2.3.10.3

Software Shutdown Details

2.3.11

Emulation

SRIO Functional Description

Power consumption is minimized for all logical blocks that are in shutdown. In addition to simply asserting

the appropriate reset signal to each logical block within the peripheral, clocks are gated off to the

corresponding logical block as well. Clocks are allowed to run for 32 clock cycles, which is necessary to

fully reset each logical block. When the appropriate logical block is fully reset, the clock input to that

subblock is gated off. When software asserts GBL_EN/BLKn_EN to release the logical block from reset,

the clocks are un-gated and the GBL_EN_STAT/BLKn_EN_STAT bit(s) indicate a value of 1b.

Note:

The BLK_EN bits allow you to shut down and gate clocks to unused portions of the logic,

while other parts of the peripheral continue to operate. When shutting down an individual

block, if TXU and RXU queues are not torn down correctly, the DMA bus could hang. For

example, setting BLK3_EN = 0 (disabling the TXU) before a teardown of the queue could

cause any outstanding DMA request returned to the peripheral for the TXU to hang the

bus.

When using the GBL_EN to shutdown/reset the entire peripheral, it is important to first stop all

master-initiated commands on the DMA bus interface. For example, if the GBL_EN is asserted in the

middle of a DMA transfer from the peripheral, this could hang the bus. The procedure to follow is:

1. Stop all RapidIO source transactions, including LSU and TXU operations. The four LSU blocks should

indiciate a BSY status of 0b (offsets 0418h, 0438h, 0458h, 0478h). If an EDMA channel is used for

driving the LSU, it must be stopped to prevent new/additional transfers. This procedure is outside the

scope of this specification. Teardown of the TXU queues is accomplished by writing 0000FFFFh to

RIO_TX_QUEUE_TEAR_DOWN (offset 0700h). Hardware will then tear down the queues and clear

these bits automatically when the teardown is complete.

2. Stop all RapidIO message receive, RXU, operations. Teardown of the RXU queues is accomplished by

writing 0000FFFFh to RIO_RX_QUEUE_TEAR_DOWN (offset 0740h). Hardware will then tear down

the queues and clear these bits automatically when complete.

3. Once teardown is complete, clear the PEREN bit of the RIO_PCR (offset 0004h) to stop all new logical

layer transactions.

4. Wait 1 second to finish any current DMA transfer.

5. Deassert GBL_EN (offset 0030h).

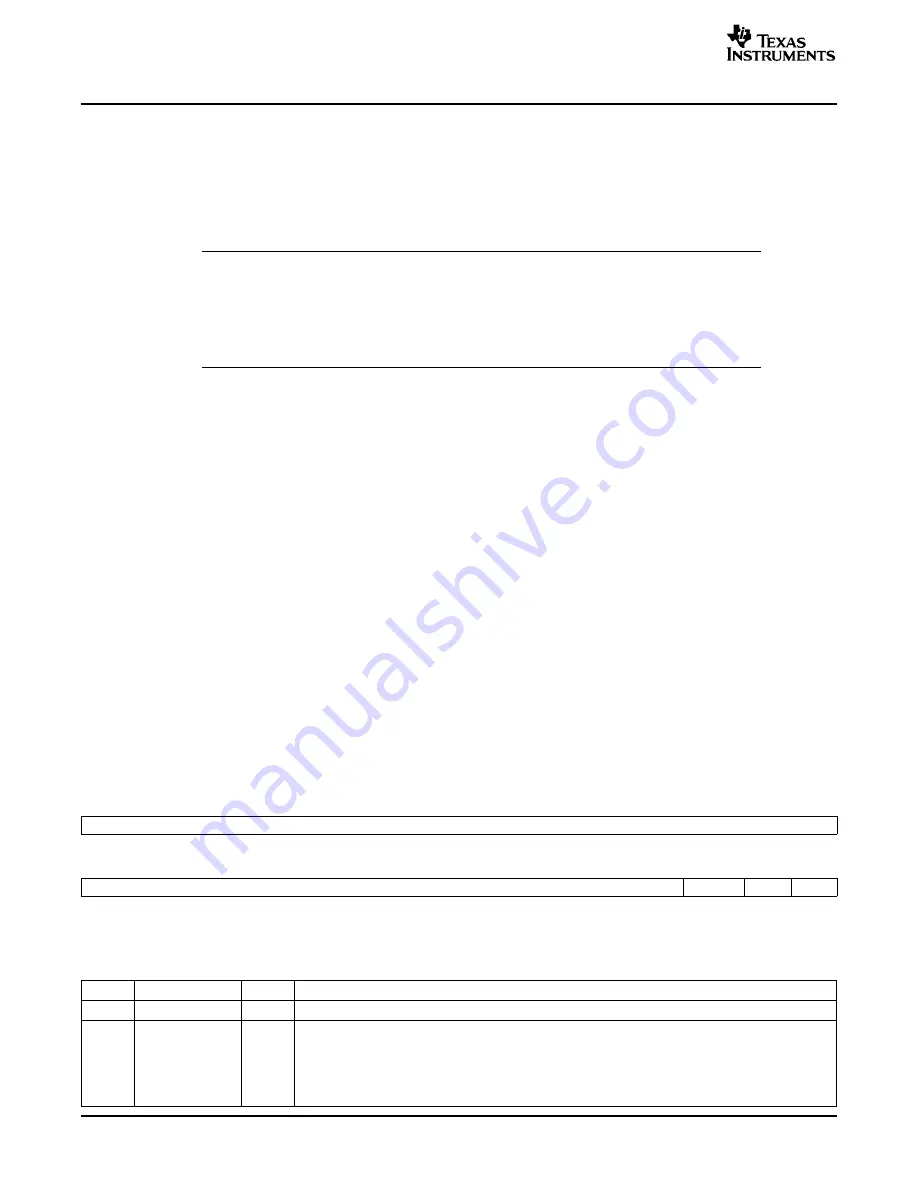

Expected behavior during emulation halt is controlled within the peripheral by the SOFT and FREE bits of

the peripheral control register (PCR). These bits are shown in

Figure 40

and described in

Table 29

.

Figure 40. Peripheral Control Register (PCR) - Address Offset 0004h

31

16

Reserved

R-0

15

3

2

1

0

Reserved

PEREN

SOFT

FREE

R-0

R/W-0

R/W-0

R/W-1

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Table 29. Peripheral Control Register (PCR) Field Descriptions

Bit

Field

Value

Description

31–3

Reserved

0

These read-only bits return 0s when read.

2

PEREN

Peripheral enable. Controls the flow of data in the logical layer of the peripheral. As an initiator, it

will prevent TX transaction generation; as a target, it will disable incoming requests. This should be

the last enable bit to toggle when bringing the device out of reset to begin normal operation.

0

Data flow control is disabled.

1

Data flow control is enabled.

74

Serial RapidIO (SRIO)

SPRUE13A – September 2006

Submit Documentation Feedback