www.ti.com

4.3.3

LSU Interrupt Condition Status and Clear Registers

Interrupt Conditions

For transmission, the clearing of any ICSR bit is dependent on the CPU writing to the CP register for the

queue (QUEUEn_TXDMA_CP). The CPU acknowledges the interrupt after reclaiming all available buffer

descriptors by writing the CP value. This value is compared against the port written value in the CP

register. If the values are equal, the interrupt is deasserted.

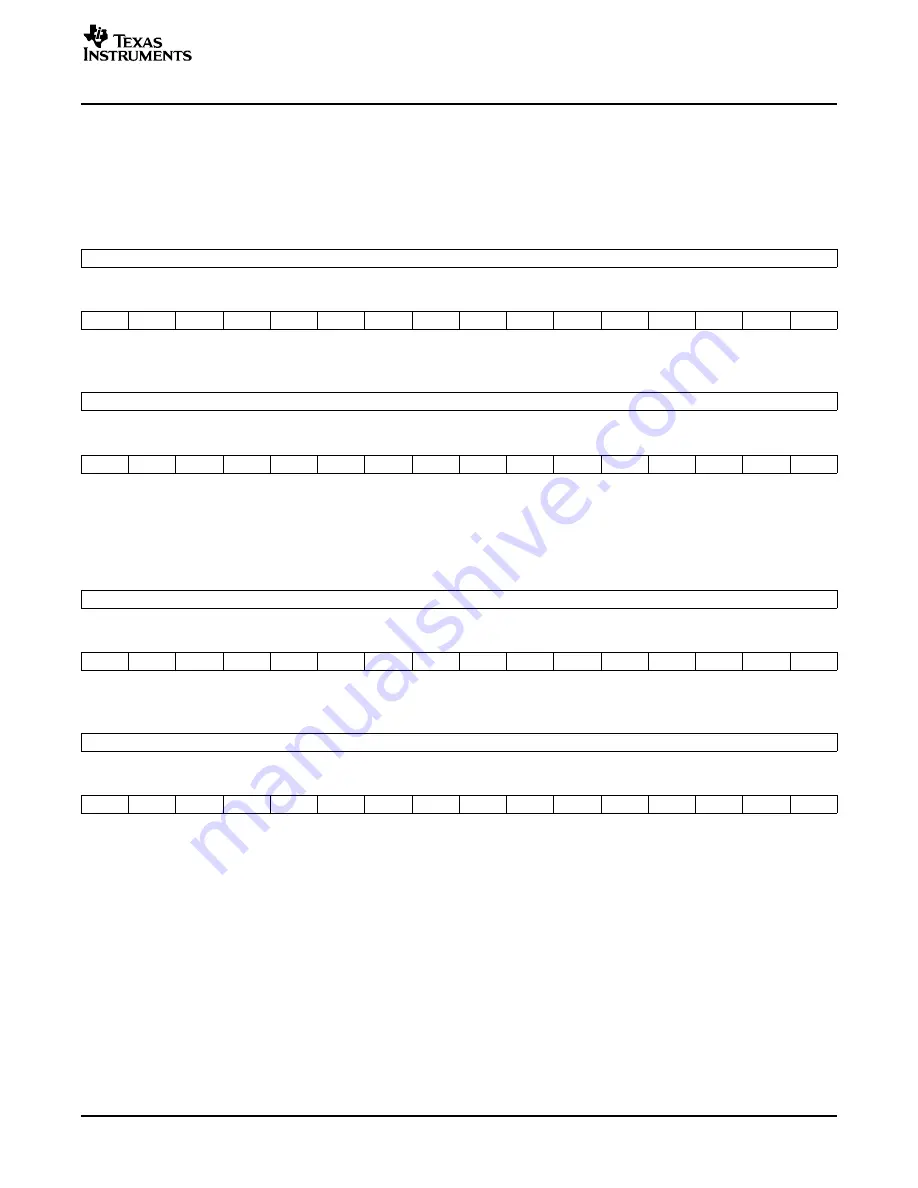

Figure 50. RX CPPI Interrupt Condition Status and Clear Registers

RX CPPI Interrupt Condition Status Register (RX_CPPI_ICSR) (Address Offset 0240h)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICS15

ICS14

ICS13

ICS12

ICS11

ICS10

ICS9

ICS8

ICS7

ICS6

ICS5

ICS4

ICS3

ICS2

ICS1

ICS0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

RX CPPI Interrupt Condition Clear Register (RX_CPPI_ICCR) (Address Offset 0248h)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICC15

ICC14

ICC13

ICC12

ICC11

ICC10

ICC9

ICC8

ICC7

ICC6

ICC5

ICC4

ICC3

ICC2

ICC1

ICC0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

LEGEND: R = Read only; W = Write only; -n = Value after reset

Figure 51. TX CPPI Interrupt Condition Status and Clear Registers

TX CPPI Interrupt Condition Status Register (TX_CPPI_ICSR) (Address Offset 0250h)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICS15

ICS14

ICS13

ICS12

ICS11

ICS10

ICS9

ICS8

ICS7

ICS6

ICS5

ICS4

ICS3

ICS2

ICS1

ICS0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

TX CPPI Interrupt Condition Clear Register (TX_CPPI_ICCR) (Address Offset 0258h)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICC15

ICC14

ICC13

ICC12

ICC11

ICC10

ICC9

ICC8

ICC7

ICC6

ICC5

ICC4

ICC3

ICC2

ICC1

ICC0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

LEGEND: R = Read only; W = Write only; -n = Value after reset

The ICSR and the ICCR for the LSUs are shown in

Figure 52

. These interrupt condition registers are used

when the SRIO peripheral transmits direct I/O packets. As described in

Table 36

, each of the status and

clear bits corresponds to a particular type of transaction interrupt condition for a particular LSU. The ICS

bits of LSU_ICSR indicate the occurrence of the conditions. The ICC bits of LSU_ICCR are used to clear

the corresponding ICS bits.

SPRUE13A – September 2006

Serial RapidIO (SRIO)

89

Submit Documentation Feedback