SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

17

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

software-programmable wait-state generator (continued)

Table 2. Software Wait-State Register (SWWSR) Bit Fields

BIT

RESET

FUNCTION

NO.

NAME

RESET

VALUE

FUNCTION

15

XPA

0

Extended program address control bit. XPA is used in conjunction with the program space fields

(bits 0 through 5) to select the address range for program space wait states.

14–12

I/O

1

I/O space. The field value (0–7) corresponds to the base number of wait states for I/O space accesses

within addresses 0000–FFFFh. The SWSM bit of the SWCR defines a multiplication factor of 1 or 2 for

the base number of wait states.

11–9

Data

1

Upper data space. The field value (0–7) corresponds to the base number of wait states for external

data space accesses within addresses 8000–FFFFh. The SWSM bit of the SWCR defines a

multiplication factor of 1 or 2 for the base number of wait states.

8–6

Data

1

Lower data space. The field value (0–7) corresponds to the base number of wait states for external

data space accesses within addresses 0000–7FFFh. The SWSM bit of the SWCR defines a

multiplication factor of 1 or 2 for the base number of wait states.

5–3

Program

1

Upper program space. The field value (0–7) corresponds to the base number of wait states for external

program space accesses within the following addresses:

XPA = 0: x8000 – xFFFFh

XPA = 1: The upper program space bit field has no effect on wait states.

The SWSM bit of the SWCR defines a multiplication factor of 1 or 2 for the base number of wait

states.

2–0

Program

1

Program space. The field value (0–7) corresponds to the base number of wait states for external

program space accesses within the following addresses:

XPA = 0: x0000–x7FFFh

XPA = 1: 00000–FFFFFh

The SWSM bit of the SWCR defines a multiplication factor of 1 or 2 for the base number of wait

states.

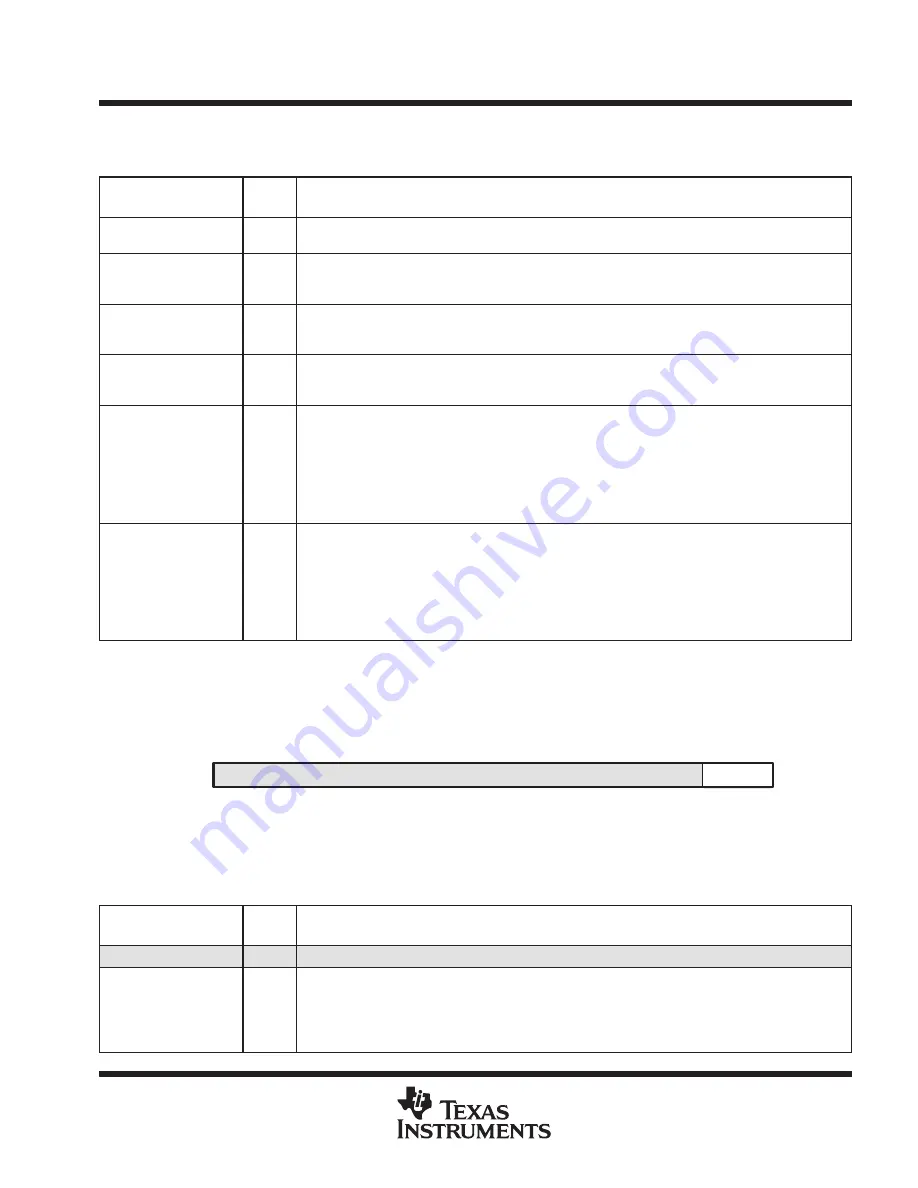

The software wait-state multiplier bit of the software wait-state control register (SWCR) is used to extend the

base number of wait states selected by the SWWSR. The SWCR bit fields are shown in Figure 5 and described

in Table 3.

Reserved

1

15

R/W-0

SWSM

0

R/W-0

LEGEND: R = Read, W = Write

Figure 5. Software Wait-State Control Register (SWCR) [MMR Address 002Bh]

Table 3. Software Wait-State Control Register (SWCR) Bit Fields

PIN

RESET

FUNCTION

NO.

NAME

RESET

VALUE

FUNCTION

15–1

Reserved

0

These bits are reserved and are unaffected by writes.

0

SWSM

0

Software wait-state multiplier. Used to multiply the number of wait states defined in the SWWSR by a factor

of 1 or 2.

SWSM = 0: wait-state base values are unchanged (multiplied by 1).

SWSM = 1: wait-state base values are mulitplied by 2 for a maximum of 14 wait states.