SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

23

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

DMA controller

The ’5402 direct memory access (DMA) controller transfers data between points in the memory map without

intervention by the CPU. The DMA controller allows movements of data to and from internal program/data

memory or internal peripherals (such as the McBSPs) to occur in the background of CPU operation. The DMA

has six independent programmable channels allowing six different contexts for DMA operation.

features

The DMA has the following features:

The DMA operates independently of the CPU.

The DMA has six channels. The DMA can keep track of the contexts of six independent block transfers.

The DMA has higher priority than the CPU for internal accesses.

Each channel has independently programmable priorities.

Each channel’s source and destination address registers can have configurable indexes through memory

on each read and write transfer, respectively. The address may remain constant, be post-incremented,

post-decremented, or be adjusted by a programmable value.

Each read or write transfer may be initialized by selected events.

Upon completion of a half-block or an entire-block transfer, each DMA channel may send an interrupt to the

CPU.

The DMA can perform double-word transfers (a 32-bit transfer of two 16-bit words).

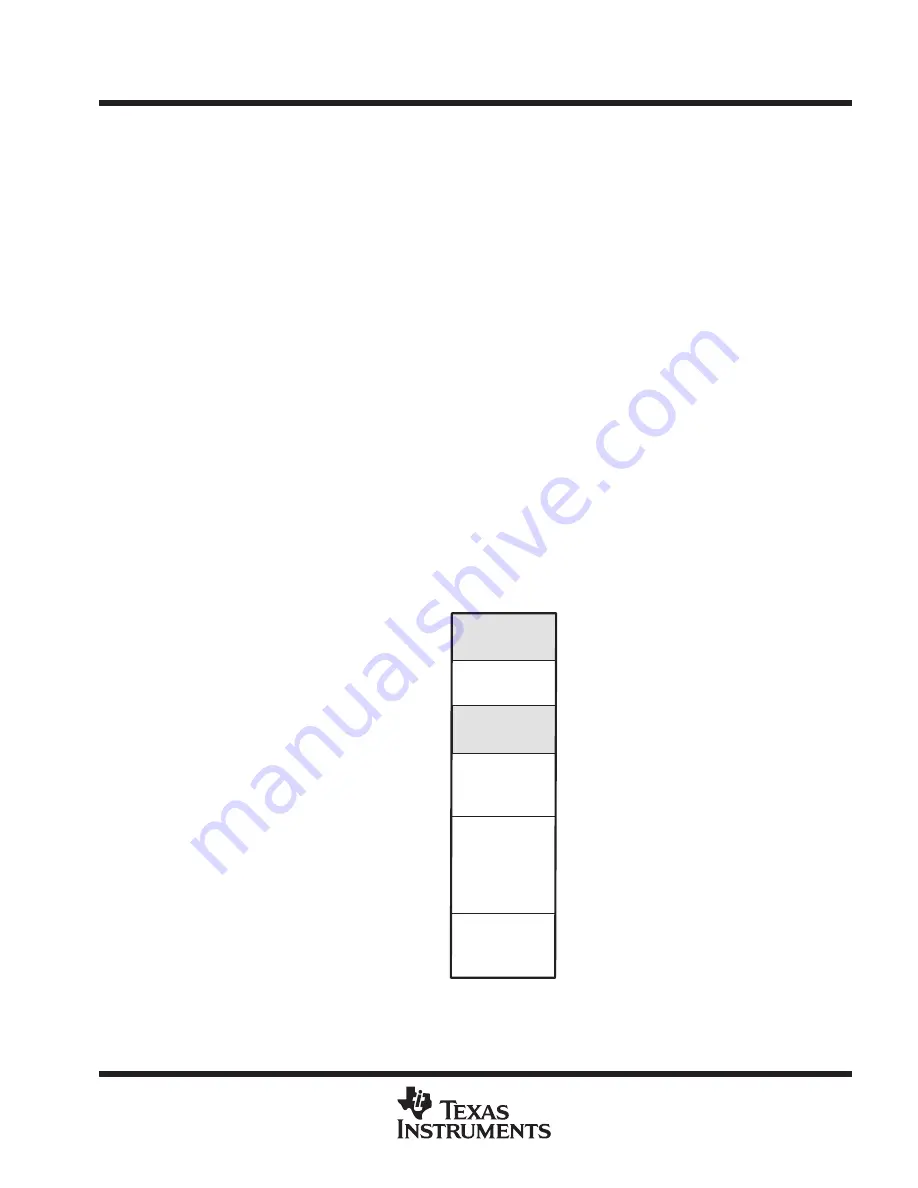

DMA memory map

The DMA memory map is shown in Figure 7 to allow DMA transfers to be unaffected by the status of the MPMC,

DROM, and OVLY bits.

FFFF

Reserved

4000

3FFF

Hex

0000

005F

0060

On-Chip DARAM

Scratch-Pad

0080

007F

(16K x 16-bit)

RAM

Reserved

McBSP

Registers

001F

0020

0023

0024

Reserved

Figure 7. ’5402 DMA Memory Map