SPRS079E – OCTOBER 1998 – REVISED AUGUST 2000

35

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

electrical characteristics over recommended operating case temperature range (unless otherwise

noted)

PARAMETER

TEST CONDITIONS

MIN

TYP†

MAX

UNIT

VOH

High-level output voltage

IOH = MAX

2.4

V

VOL

Low-level output voltage

IOL = MAX

0.4

V

IIZ

Input current for

outputs in high

D[15:0], HD[7:0]

Bus holders enabled, DVDD = MAX,

VI = VSS to DVDD

–175

175

µ

A

IIZ

out uts

in

high

impedance

All other inputs

DVDD = MAX, VO = VSS to DVDD

–5

5

µ

A

X2/CLKIN

–40

40

TRST

With internal pulldown

–5

300

II

Input current

HPIENA

With internal pulldown

(VI = VSS

–5

300

µ

A

II

u cu e

TMS, TCK, TDI, HPI

With internal pullups,

HPIENA = 0

( I

SS

to DVDD)

–300

5

µ

A

All other input only pins

5

5

All other input-only pins

–5

5

IDDC

Supply current, core CPU

CVDD = 1.8 V, fclock = 100 MHz¶, TC = 25

°

C#

45

mA

IDDP

Supply current, pins

DVDD = 3.3 V, fclock = 100 MHz¶, TC = 25

°

C||

30

mA

IDD

Supply current,

IDLE2

PLL

×

1 mode,

100 MHz input

2

mA

IDD

Su

ly current,

standby

IDLE3

Divide-by-two mode, CLKIN stopped

20

µ

A

Ci

Input capacitance

5

pF

Co

Output capacitance

5

pF

† All values are typical unless otherwise specified.

‡ All revisions of the ’5402 can be operated with an external clock source, provided that the proper voltage levels be driven on the X2/CLKIN pin.

It should be noted that the X2/CLKIN pin is referenced to the device 1.8V power supply (CVdd), rather than the 3V I/O supply (DVdd). Refer to

the recommended operating conditions section of this document for the allowable voltage levels of the X2/CLKIN pin.

§ HPI input signals except for HPIENA.

¶ Clock mode: PLL

×

1 with external source

# This value represents the current consumption of the CPU, on-chip memory, and on-chip peripherals. Conditions include: program execution

from on-chip RAM, with 50% usage of MAC and 50% usage of NOP instructions. Actual operating current varies with program being executed.

|| This value was obtained using the following conditions: external memory writes at a rate of 20 million writes per second, CLKOFF=0, full-duplex

operation of McBSP0 and McBSP1 at a rate of 10 million bits per second each, and 15-pF loads on all outputs. For more details on how this

calculation is performed, refer to the

Calculation of TMS320C54x Power Dissipation Application Report (literature number SPRA164).

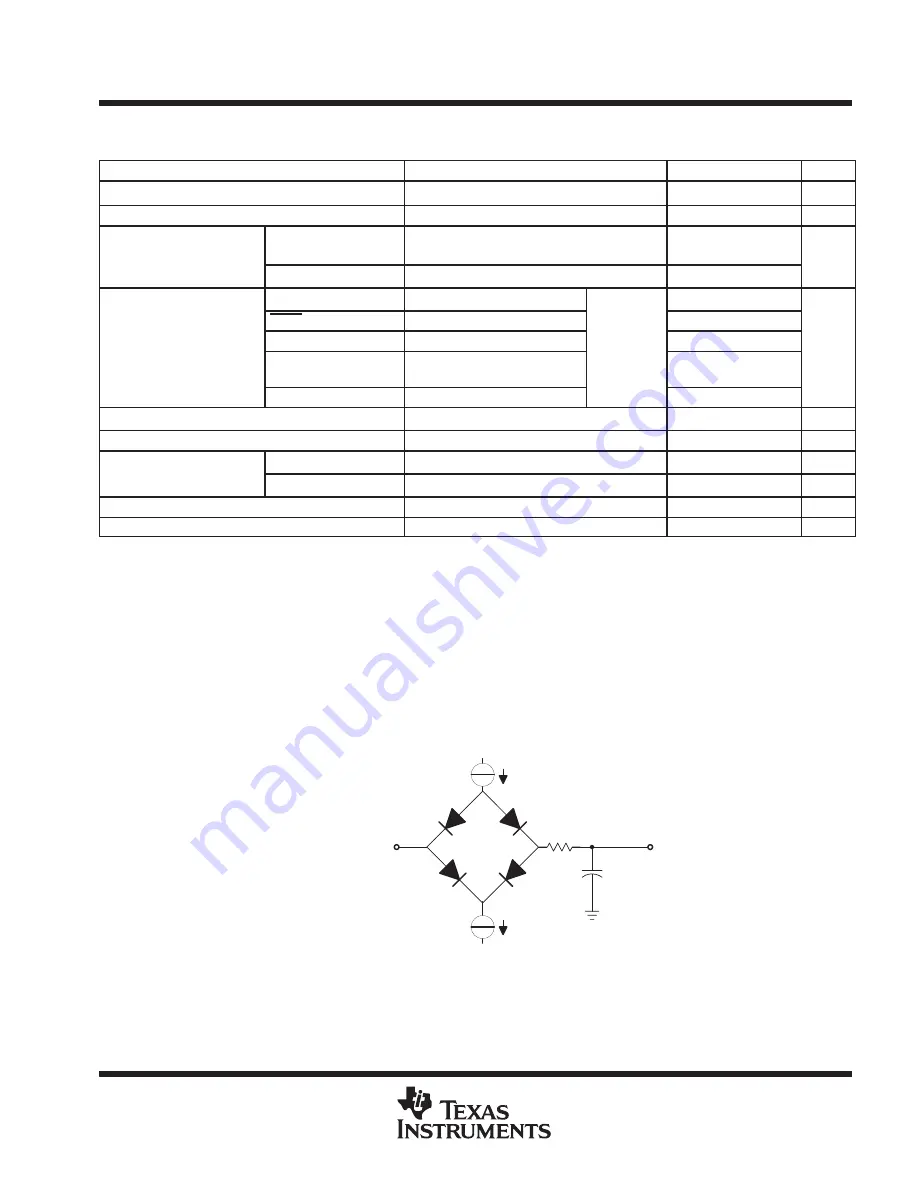

PARAMETER MEASUREMENT INFORMATION

Tester Pin

Electronics

VLoad

IOL

C

T

IOH

Output

Under

Test

50

Ω

Where:

IOL

= 1.5 mA (all outputs)

IOH

= 300

µ

A (all outputs)

VLoad = 1.5 V

CT

= 40 pF typical load circuit capacitance

Figure 9. 3.3-V Test Load Circuit