TSTABLE

VSRCNEW (max)

Old Voltage

New Voltage

Time

V

oltage

SRPOS

VSRCNEW (min)

VSRCVALID (min)

VSRCVALID (max)

43

SLVSDC2B – FEBRUARY 2016 – REVISED AUGUST 2016

Product Folder Links:

Copyright © 2016, Texas Instruments Incorporated

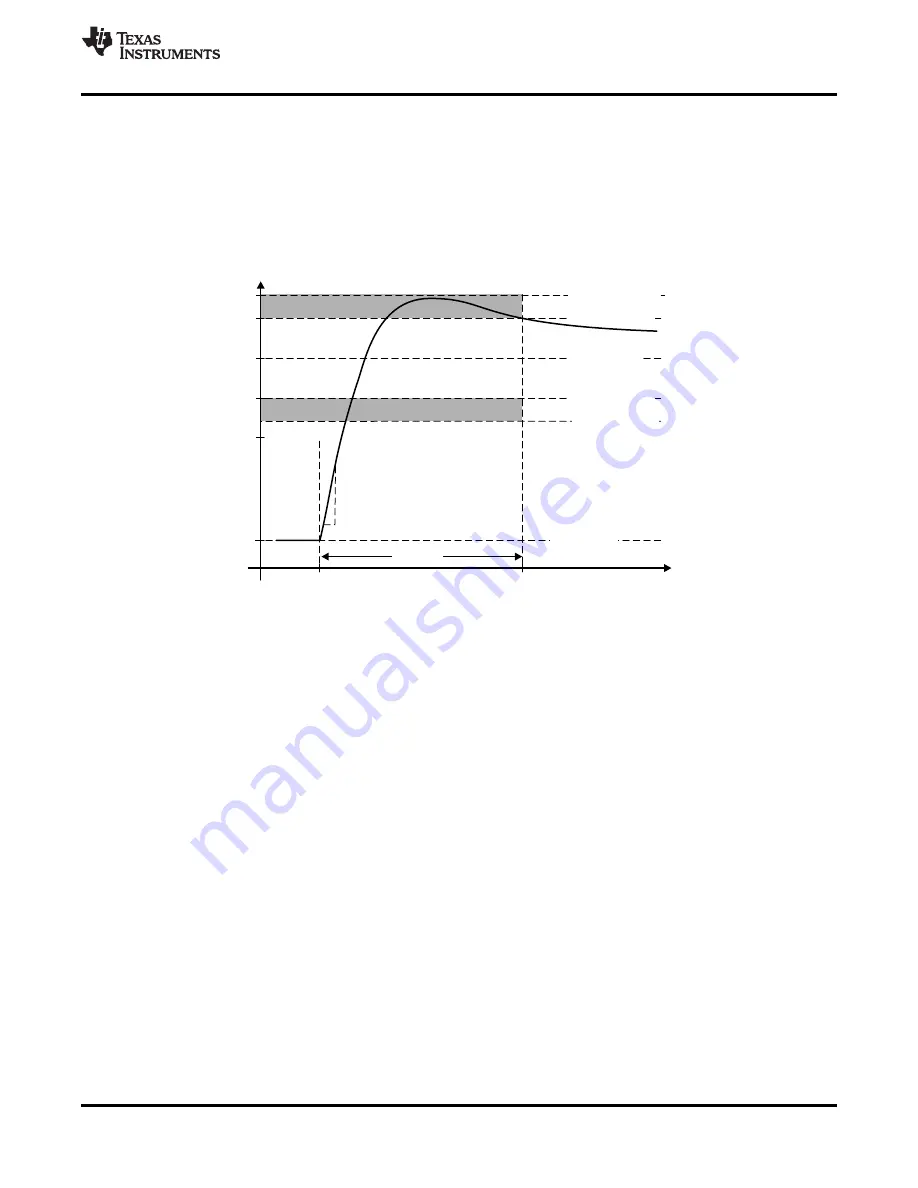

9.3.3.18 Voltage Transitions on VBUS through Port Power Switches

shows the waveform for a positive voltage transition. The timing and voltages apply to both a transition

from 0 V to PP_5V0 and a transition from PP_5V0 to PP_HV as well as a transition from PP_5V0 to an PP_EXT.

A transition from PP_HV to PP_EXT is possible and vice versa, but does not necessarily follow the constraints in

. When a switch is closed to transition the voltage, a maximum slew-rate of SRPOS occurs on the

transition. The voltage ramp will remain monotonic until the voltage reaches VSRCVALID within the final voltage.

The voltage may overshoot the new voltage by VSRCVALID. After time TSTABLE from the start of the transition,

the voltage will fall to within VSRCNEW of the new voltage. During the time TSTABLE, the voltage may fall below

the new voltage, but will remain within VSRCNEW of this voltage.

Figure 34. Positive Voltage Transition on VBUS

shows the waveform for a negative voltage transition. The timing and voltages apply to both a

transition from PP_HV to PP_5V0 and a transition from PP_5V0 to 0V as well as a transition from PP_EXT to

PP_5V0. A transition from PP_HV to PP_EXT is possible and vice versa, but does not necessarily follow the

constraints in

. When a switch is closed to transition the voltage, a maximum slew-rate of SRNEG

occurs on the transition. The voltage ramp will remain monotonic until the voltage reaches TOLTRANUN within

the final voltage. The voltage may overshoot the new voltage by TOLTRANLN. After time TSTABLE from the

start of the transition, the voltage will fall to within VSRCNEW of the new voltage. During the time TSTABLE, the

voltage may fall below the new voltage, but will remain within VSRCNEW of this voltage.