76

SLVSDC2B – FEBRUARY 2016 – REVISED AUGUST 2016

Product Folder Links:

Copyright © 2016, Texas Instruments Incorporated

10.2.1.2.3

Oscillator (R_OSC) Resistor

A 15-k

Ω

0.1% resistor is needed for key PD BMC communication timing and the USB2.0 endpoint. A 1% 15-k

Ω

resistor is not recommended to be used because the internal oscillators are not controlled well enough by this

loose resistor tolerance.

10.2.1.2.4

VBUS Capacitor and Ferrite Bead

A 1-µF ceramic capacitor is placed close to the TPS65981 VBUS pins. A 6-A ferrite bead is used in this design

along with four high frequency noise 10-nF capacitors placed close to the Type-C connector to minimize noise.

10.2.1.2.5

Soft Start (SS) Capacitor

The recommended 0.22-µF capacitor is placed on the TPS65981 SS pin.

10.2.1.2.6

USB Top (C_USB_T), USB Bottom (C_USB_B), and Sideband-Use (SBU) Connections

Although the charger is configured to be only a power source, SBU1/2, USB top and bottom must be routed to

the Type C connector. This allows for debugging or for any specific alternate modes for power to be configured if

needed. ESD protection is used in the design on all of these nets as good design practice.

10.2.1.2.7

Port Power Switch (PP_EXT, PP_HV, PP_5V0, and PP_CABLE) Capacitors

The design assumes that a DC-DC converter is connected to the paths where there is significant output

capacitance on the DC-DCs to provide the additional capacitance for load steps. TI recommends for the DC-DC

converters to be capable of supporting current spikes which can occur with certain PD configurations.

The PP_EXT path is capable of supporting up to 5 A which requires additional capacitance to support system

loading by the device connected to the charger. A ceramic 10-µF (X7R/X5R) capacitor is used in this design.

This capacitor must at least have a 25 V rating and TI recommends to have 30 V or greater rated capacitor.

The PP_HV path is capable of supporting up to 3 A which requires additional capacitance to support system

loading by the device connected to the charger. A ceramic 10-µF (X7R/X5R) capacitor coupled with a 0.1 µF

high frequency capacitor is placed close to the TPS65981.

The PP_5V0 and PP_CABLE supplies are connected together therefore a ceramic 22-µF (X7R/X5R) capacitor

coupled with a 0.1-µF high-frequency capacitor is placed close to the TPS65981. The PP_5V0 path can support

3 A and the PP_CABLE path supports 600 mA for active Type C PD cables.

The design assumes that a DC-DC converter is connected to the paths where there is significant output

capacitance on the DC-DCs to provide the additional capacitance. TI recommends that the DC-DC converters

are capable of supporting current spikes which can occur with certain PD configurations.

10.2.1.2.8

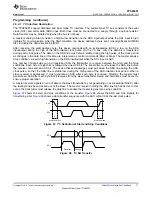

Cable Connection (CCn) Capacitors and RPD_Gn Connections

This charger application is designed to only be a source of power and does not support dead battery. RPD_G1

and RPD_G2 must be tied to GND and not connected to the CC1 and CC2 respectively. For CC1 and CC2 lines,

they require a 330-pF capacitor to GND.

10.2.1.2.9

LDO_3V3, LDO_1V8A, LDO_1V8D, LDO_BMC, VIN_3V3, and VDDIO

For all capacitances, consider the DC-voltage derating of ceramic capacitors. Generally the effective capacitance

is halved with voltage applied.

VIN_3V3 is connected to VDDIO which ensures that the I/Os of the TPS65981 will be configured to 3.3 V. A 1-µF

capacitor is used and is shared between VDDIO and VIN_3V3. LDO_1V8D, LDO_1V8A, and LDO_BMC each

have a 1-µF capacitor. In this design LDO_3V3 powers the external flash and various pull-ups of the TPS65981

device. A 10-µF capacitor was chosen to support these additional connections.