Barrel Jack Detect

and PFET Enable

100 kΩ

10 kΩ

1.81 V

20 V

DC Barrel Jack

79

SLVSDC2B – FEBRUARY 2016 – REVISED AUGUST 2016

Product Folder Links:

Copyright © 2016, Texas Instruments Incorporated

10.2.2.2.1

Port Power Switch (PP_5V0 and PP_CABLE) Capacitors

The PP_5V0 supply is un-used in this application because 5 Volts is the default output voltage of the variable

buck regulator and is sourced to VBUS from PP_HV. PP_CABLE is still used and can supply up to 500 mA to

provide power to e-marked or active Type-C cables for SuperSpeed data signal conditioning. The PP_CABLE

supply, when PP_5V0 is un-used, is connected to a 4.7-µF ceramic (X7R/X5R) capacitor coupled with a 0.1-µF

high-frequency capacitor that must be placed close to the TPS65981.

10.2.2.2.2

HD3SS460 Control and DisplayPort Configuration

The Type-C port in this design supports DisplayPort and/or USB3.1 SuperSpeed data by adding the HD3SS460

multiplexer with GPIO input signals controlled by the TPS65981.

shows the DisplayPort configurations

supported in the system.

shows the summary of the TPS65981 GPIO signals control for the

HD3SS460. The HD3SS460 is also capable of multiplexing the required signals to the SBU_1/2 pins at the Type-

C port.

Table 13. Supported DisplayPort Configurations

DisplayPort Role

Display Port

Pin Assignment

DisplayPort Lanes

Configuration 1

UFP_D

Pin Assignment C

4-Lane

Configuration 2

UFP_D

Pin Assignment D

2-Lane and USB 3.1 data

(1)

Specific GPIO pins are used for simplicity, but the configurable firmware settings allow the HD3SS460 GPIO Events to be mapped to

any GPIO pin of the TPS65981.

Table 14. TPS65981 and HD3SS460 GPIO Control

(1)

TPS65981 GPIO

HD3SS460 Control Pin

Description

GPIO0

AMSEL

Alternate Mode Selection (4-Lane DP/2-Lane DP + USB3.1)

GPIO3

EN

Super Speed Multiplexer Enable

DEBUG1

POL

Type-C Cable Orientation

10.2.2.2.3

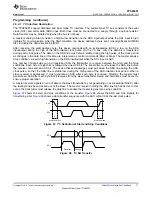

AC-DC Power Supply (Barrel Jack) Detection Circuitry

The system is design to either operate bus-powered over Type-C/PD or line-powered from the DC barrel jack.

The TPS65981 detects that the DC barrel jack is connected to GPIOn. In the simplest form, a voltage divider

could be set to the GPIO I/O level when the DC Barrel jack voltage is present, as shown in

. A

comparator circuit is recommend and used in this design for design robustness, as shown in

shows the barrel jack detection circuitry used in the dock or monitor application connected to GPIO2 configured

as an input.

Figure 77. DC Barrel Jack Voltage Divider