85

SLVSDC2B – FEBRUARY 2016 – REVISED AUGUST 2016

Product Folder Links:

Copyright © 2016, Texas Instruments Incorporated

Layout Guidelines (continued)

12.1.5 Routing PP_HV, PP_EXT, PP_5V0, and VBUS

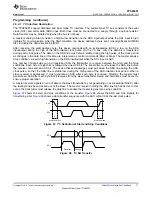

On the top layer, create pours for PP_HV, PP_5V0 and VBUS to extend area to place 8 mil hole and 16 mil

diameter vias to connect to the bottom layer. A minimum of 4 vias is needed to connect between the top and

bottom layer. For the bottom layer, place pours that will connect the PP_HV, PP_5V0, and VBUS capacitors to

their respective vias. The external FETS connected from PP_EXT to VBUS (SENSEP, SENSEN, HV_GATE1,

and HV_GATE2 pins of the TPS65981) must also be connected through pours and place vias for the external

FET gates. For 5 A systems, special consideration must be taken for ensuring enough copper is used to handle

the higher current. For 0.5 oz copper top or bottom pours with 0.5-oz plating use approximately a 120-mil pour

width for 5-A support. When routing the 5 A through a 0.5 oz internal layer, more than 200 mil is required to carry

the current.

and

show the pours used in this example.

12.1.6 Routing Top and Bottom Passive Components

The next step is to route the connections to the passive components on the top and bottom layers. For the top

layer only CC1 and CC2 capacitors will be placed on top. Routing the CC1 and CC2 lines with a 8 mil trace will

facilitate the needed current for supporting powered Type C cables through VCONN. For more information on

VCONN please refer to the Type C specification.

shows how to route to the CC1 and CC2 to their

respective capacitors. For capacitor GND pin use a 10 mil trace if possible. This particular system support Dead

Battery, which has RPD_G1/2 connected to CC1/2.

The top layer pads will have to be connected the bottom placed component through Vias (8 mil hole and 16 mil

diameter recommended). For the VIN_3V3, VDDIO, LDO_3V3, LDO_1V8A, LDO1 V8D, and LDO_BMC use 6mil

traces to route. For PP_CABLE route using an 8 mil trace and for all other routes 4 mil traces may be used. To

allow for additional space for routing, stagger the component vias to leave room for routing other signal nets.

and

show the top and bottom routing.

provides a summary of the trace widths.

Table 16. Routing Trace Widths

ROUTE

WIDTH (mil)

CC1, CC2, PP_CABLE

8

LDO_3V3, LDO_1V8A, LDO_1V8D, LDO_BMC, VIN_3V3, VDDIO,

HV_GATE1, HV_GATE2

6

Thermal Pad (GND)

10

12.1.7 Thermal Pad Via Placement

The Thermal Pad under the TPS65981 is populated with 20 for thermal relief vias that must be electrically

connected to GND. This can be seen in the

that is not connected to a PCB project. If any of the vias in

the footprint are removed for placing components closer to the TPS65981, a minimum of 6 vias must be used for

thermal dissipation to the GND planes. If the number of Thermal Relief vias is reduced, the majority of these vias

must be placed on the right side of the device by the power path.

12.1.8 Top Layer Routing

Once the components are routed, the rest of the area can be used to route all of the additional I/O. After all nets

have been routed place polygonal pours around the PP_5V0, PP_HV, and VBUS pins of the TPS65981 GND

pins to the GND vias. Refer to

for the final top routing.

12.1.9 Inner Signal Layer Routing

The inner signal layer is used to route the I/O, low-speed data signals, and the external FET control and sensing

of the TPS65981 away from the critical thick power traces and length-sensitive high-speed data

shows

how to route the internal layer.

12.1.10 Bottom Layer Routing

The bottom layer has most of the components placed and routed already. Place a polygon pour to connect all of

the GND nets and vias on the bottom layer, refer to