LDO

LDO_1V8D

EN

LDO_3V3_VB_EN

LDO

VREF

S2

S1

Digitally

adjustable

trip Point

VREF

EN

LDO_1V8D_EN

LDO

VREF

LDO_1V8A

VBUS

EN

LDO_1V8A_EN

VREF

VIN_3V3

LDO_3V3

To Digital Core

VRSTZ_3V3

Copyright © 2016, Texas Instruments Incorporated

54

SLVSDC2B – FEBRUARY 2016 – REVISED AUGUST 2016

Product Folder Links:

Copyright © 2016, Texas Instruments Incorporated

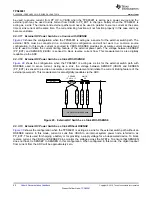

Figure 49. Power Supply Path

The TPS65981 is powered from either VIN_3V3 or VBUS. The normal power supply input is VIN_3V3. In this

mode, current flows from VIN_3V3 to LDO_3V3 to power the core 3.3-V circuitry and the 3.3-V I/Os. A second

LDO steps the voltage down from LDO_3V3 to LDO_1V8D and LDO_1V8A to power the 1.8-V core digital

circuitry and 1.8-V analog circuits. When VIN_3V3 power is unavailable and power is available on the VBUS, the

TPS65981 will be powered from VBUS. In this mode, the voltage on VBUS is stepped down through an LDO to

LDO_3V3. Switch S1 in

is unidirectional and no current will flow from LDO_3V3 to VIN_3V3. When

VIN_3V3 is unavailable, this is an indicator that there is a dead-battery or no-battery condition.

9.3.5.1 Power-On and Supervisory Functions

A power-on-reset (POR) circuit monitors each supply. This POR allows active circuitry to turn on only when a

good supply is present. In addition to the POR and supervisory circuits for the internal supplies, a separate

programmable voltage supervisor monitors the VRSTZ_3V3 voltage.

9.3.5.2 Supply Switch-Over

VIN_3V3 takes precedence over VBUS, meaning that when both supply voltages are present the TPS65981 will

power from VIN_3V3. Refer to The

for a diagram showing the power supply path block. There are two

cases in with a power supply switch-over will occur. The first is when VBUS is present first and then VIN_3V3

becomes available. In this case, the supply will automatically switch-over to VIN_3V3 and brown-out prevention

is verified by design. The other way a supply switch-over will occur is when both supplies are present and

VIN_3V3 is removed and falls below 2.85 V. In this case, a hard reset of the TPS65981 occurs prompting a re-

boot.

9.3.5.3 RESETZ and MRESET

The VIN_3V3 voltage is connected to VRSTZ_3V3 by a single FET switch (S2 in

The enabling of the switch is controlled by the core digital circuitry and the conditions are programmable. A

supervisor circuit monitors the voltage at VRSTZ_3V3 for an under-voltage condition and sets the external

indicator RESETZ. The RESETZ pin is active low (low when an under-voltage condition occurs). The RESETZ

output is also asserted when the MRESET input is asserted. The MRESET input is active-high by default, but is

configurable to be active low.

shows the RESETZ timing with MRESET set to active high. When

VRSTZ_3V3 is disabled in application code, a resistance of RPDOUT_3V3 pulls down on the pin.