CH1_D4

CH1_D5

CH1_D6

CH1_D7

CH1_D8

CH1_D9

CH1_D10

CH1_D1

1

CH1_D0

CH1_D1

CH1_D2

CH1_D3

CH1_D12

CH1_D13

CH3_D6

CH3_D7

CH3_D8

CH3_D9

CH3_D10

CH3_D1

1

CH3_D12

CH3_D13

CH3_D1

CH3_D2

CH3_D3

CH3_D4

CH3_D5

CH3_D14

CH3_D15

CH4_D6

CH4_D7

CH4_D8

CH4_D9

CH4_D10

CH4_D1

1

CH4_D12

CH4_D13

CH4_D1

CH4_D2

CH4_D3

CH4_D4

CH4_D5

CH2_D6

CH2_D7

CH2_D8

CH2_D9

CH2_D10

CH2_D1

1

CH2_D12

CH2_D13

CH2_D0

CH2_D1

CH2_D2

CH2_D3

CH2_D4

CH2_D5

CH1-D0

CH1-D1

CH1-D2

CH1-D3

CH1-D4

CH1-D5

CH1-D6

CH1-D7

CH1-D8

CH1-D9

CH1-D10

CH1-D1

1

CH1-D12

CH1-D13

CH2-D0

CH2-D1

CH2-D2

CH2-D3

CH2-D4

CH2-D5

CH2-D6

CH2-D7

CH2-D9

CH2-D1

1

CH2-D12

CH2-D13

CH2-D14

CH2-D15

CH4-D1

CH1_CLKOUT

CH1-CLKOUT

CH3_CLKOUT

CH2_CLKOUT

CH4_CLKOUT

CH2-D10

CH2-D8

CH4-D2

CH4-D3

CH4-D4

CH4-D5

CH4-D6

CH4-D7

CH4-D8

CH4-D9

CH4-D10

CH4-D1

1

CH4-D12

CH4-D13

CH3-D1

CH3-D2

CH3-D3

CH3-D4

CH3-D5

CH3-D6

CH3-D7

CH3-D8

CH3-D9

CH3-D10

CH3-D1

1

CH3-D12

CH3-D13

CH3-D14

CH3-D15

CH3_D0

CH3-D0

CH4-D0

CH4_D0

CH2_D14

CH2_D15

CH2-CLKOUT

CH4-CLKOUT

CH3-CLKOUT

CH5_CLKOUT

CH5_D0

CH5_D1

CH5_D2

CH5_D3

CH5_D4

CH5_D5

CH5_D6

CH5_D7

CH5_D8

CH5_D9

CH5_D10

CH5_D1

1

CH5_D12

CH5_D13

CH6_D10

CH6_D1

1

CH6_CLKOUT

CH6_D12

CH6_D0

CH6_D13

CH6_D1

CH6_D2

CH6_D3

CH6_D4

CH6_D5

CH6_D6

CH6_D7

CH6_D8

CH6_D9

CH7_D10

CH7_D1

1

CH7_CLKOUT

CH7_D12

CH7_D0

CH7_D13

CH7_D1

CH7_D2

CH7_D3

CH7_D4

CH7_D5

CH7_D6

CH7_D7

CH7_D8

CH7_D9

CH8_D10

CH8_D1

1

CH8_CLKOUT

CH8_D12

CH8_D0

CH8_D13

CH8_D1

CH8_D2

CH8_D3

CH8_D4

CH8_D5

CH8_D6

CH8_D7

CH8_D8

CH8_D9

CH5-CLKOUT

SH3

CH5-D0

SH3

CH5-D1

SH3

CH5-D2

SH3

CH5-D3

SH3

CH5-D4

SH3

CH5-D5

SH3

CH5-D6

SH3

CH5-D7

SH3

CH5-D9

SH3

CH5-D10

SH3

CH5-D1

1

SH3

CH5-D12

SH3

CH5-D13

SH3

CH5-D8

SH3

CH6-D1

SH3

CH6-D2

SH3

CH6-D3

SH3

CH6-CLKOUT

SH3

CH6-D4

SH3

CH6-D5

SH3

CH6-D6

SH3

CH6-D7

SH3

CH6-D9

SH3

CH6-D10

SH3

CH6-D1

1

SH3

CH6-D12

SH3

CH6-D13

SH3

CH6-D8

SH3

CH6-D0

SH3

CH7-D1

SH3

CH7-D2

SH3

CH7-D3

SH3

CH7-CLKOUT

SH3

CH7-D4

SH3

CH7-D5

SH3

CH7-D6

SH3

CH7-D7

SH3

CH7-D9

SH3

CH7-D10

SH3

CH7-D1

1

SH3

CH7-D12

SH3

CH7-D13

SH3

CH7-D8

SH3

CH7-D0

SH3

CH8-D1

SH2

CH8-D2

SH2

CH8-D3

SH2

CH8-CLKOUT

SH2

CH8-D4

SH2

CH8-D5

SH2

CH8-D6

SH2

CH8-D7

SH2

CH8-D9

SH2

CH8-D10

SH2

CH8-D1

1

SH2

CH8-D12

SH2

CH8-D13

SH2

CH8-D8

SH2

CH8-D0

SH2

RN16

22ohm

RN16

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

RN8

22ohm

RN8

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

FD2

SMT

FIDUCIAL

FD2

SMT

FIDUCIAL

J20

HDR16X2MALE.100CTR

<TI_SILKTEXT>

J20

HDR16X2MALE.100CTR

<TI_SILKTEXT>

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

RN4

22ohm

RN4

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

R61

22

R61

22

RN15

22ohm

RN15

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

R63

22

R63

22

R60

22

R60

22

J5

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

J5

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

33

34

35

36

37

38

39

40

RN6

22ohm

RN6

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

J18

HDR16X2MALE.100CTR

<TI_SILKTEXT>

J18

HDR16X2MALE.100CTR

<TI_SILKTEXT>

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

J6

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

J6

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

33

34

35

36

37

38

39

40

RN14

22ohm

RN14

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

RN5

22ohm

RN5

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

RN10

22ohm

RN10

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

R62

22

R62

22

RN13

22ohm

RN13

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

RN2

22ohm

RN2

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

R29

22

R29

22

J21

HDR16X2MALE.100CTR

<TI_SILKTEXT>

J21

HDR16X2MALE.100CTR

<TI_SILKTEXT>

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

FD1

SMT

FIDUCIAL

FD1

SMT

FIDUCIAL

RN1

1

22ohm

RN1

1

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

FD3

SMT

FIDUCIAL

FD3

SMT

FIDUCIAL

R30

22

R30

22

RN3

22ohm

RN3

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

J4

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

J4

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

33

34

35

36

37

38

39

40

RN12

22ohm

RN12

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

J19

HDR16X2MALE.100CTR

<TI_SILKTEXT>

J19

HDR16X2MALE.100CTR

<TI_SILKTEXT>

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

R28

22

R28

22

RN9

22ohm

RN9

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

U1-3

XC4VLX25-SF363-BGA

U1-3

XC4VLX25-SF363-BGA

IO_L1P_6

B6

IO_L1N_6

A6

IO_L2P_6

A5

IO_L2N_6

B5

IO_L3P_6

C6

IO_L3N_6

C5

IO_L4P_6

B4

IO_L4N_VREF_6

C4

IO_L5P_6

D5

IO_L5N_6

E5

IO_L6P_6

A3

IO_L6N_6

B3

IO_L7P_6

D4

IO_L7N_6

D3

IO_L8P_CC_LC_6

B2

IO_L8N_CC_LC_6

C1

IO_L9P_CC_LC_6

F3

IO_L9N_CC_LC_6

E3

IO_L10P_6

C3

IO_L10N_6

C2

IO_L1

1P_6

F5

IO_L1

1N_6

F4

IO_L12P_6

D2

IO_L12N_VREF_6

E2

IO_L13P_6

G5

IO_L13N_6

G4

IO_L14P_6

E1

IO_L14N_6

F1

IO_L15P_6

H5

IO_L15N_6

H4

IO_L16P_6

F2

IO_L16N_6

G2

IO_L17P_6

J4

IO_L17N_6

J3

IO_L18P_6

H1

IO_L18N_6

G1

IO_L19P_6

J6

IO_L19N_6

J5

IO_L20P_6

H3

IO_L20N_VREF_6

H2

IO_L21P_6

K5

IO_L21N_6

K4

IO_L22P_6

K1

IO_L22N_6

J2

IO_L23P_VRN_6

L5

IO_L23N_VRP_6

L4

IO_L24P_CC_LC_6

K3

IO_L24N_CC_LC_6

K2

IO_L25P_CC_LC_6

M4

IO_L25N_CC_LC_6

M3

IO_L26P_6

M1

IO_L26N_6

L1

IO_L27P_6

M6

IO_L27N_6

M5

IO_L28P_6

M2

IO_L28N_VREF_6

L2

IO_L29P_6

N5

IO_L29N_6

N4

IO_L30P_6

N3

IO_L30N_6

N2

IO_L31P_6

P5

IO_L31N_6

P4

IO_L32P_6

P2

IO_L32N_6

P1

R27

22

R27

22

J3

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

J3

HEADERMALE20x2POS.100VER

T

DA

T

A_OUT

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

3

5

7

9

1

1

13

15

17

19

21

23

25

27

29

31

33

34

35

36

37

38

39

40

RN17

22ohm

RN17

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

RN7

22ohm

RN7

22ohm

1

16

2

15

3

14

4

13

5

12

6

1

1

7

10

8

9

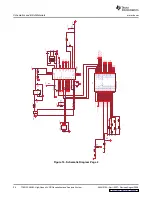

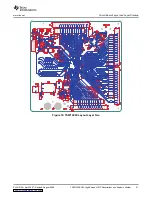

www.ti.com

Schematics and Bill of Materials

Figure 17. Schematic Diagram Page 5

SLAU212A – April 2007 – Revised August 2008

TSW1200EVM: High-Speed LVDS Deserializer and Analysis System

27