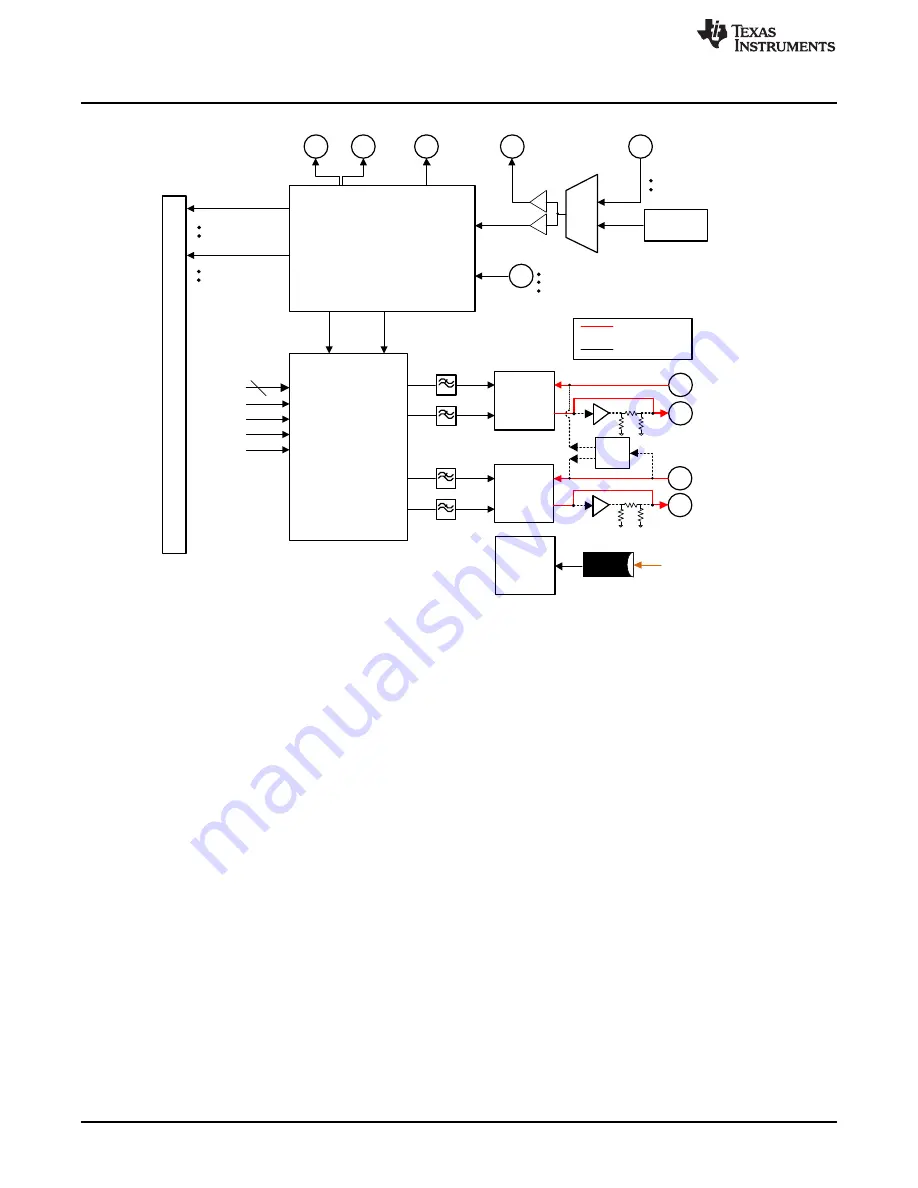

10MHz

TCXO

LMK04806B

DAC34H84

DAC_CLK

(LVPECL

AC

Coupled)

OSTR_CLK

(LVPECL AC

Coupled)

FPGA CLK 1

TSW1400/TSW3100

LVDS AC coupled

TRF3705

Default TRF3705 Output

6V Only

J18

Power Supply

Circuits

TRF3705

Default TRF3705 Output

A

B

C

D

J12

Ext. CLK Input

2.4-Vpp MaxSingle Ended

3.1GHz Max

AC coupled

Reference

LVCMOS Level

Reference for LMK04806B PLL

Mode

FPGA CLK 2

TSW1400

LVDS AC coupled

J11

J16

J5

J2

J3

MUX

3dB

Splitter

RF

RF

LO

LO

Q

Q

I

I

J7

J9

J1

9

J22

RF1

RF2

LO

1

LO2

Default Path

Optional Path

J1

3

H

ig

h

Sp

e

e

d

Sa

mt

e

c

C

o

n

n

e

ct

o

r

C

L

K

0

p

C

L

K

0

n

C

L

K

6

p

CLK8p

CLK8n

CLK9p

CLK9n

OSCIN

CLKIN

1

REF In

REF Out

CLKOUTP

CLKOUTP

CLKOUTN

C

L

K

4

p

C

L

K

4

n

C

L

K

3

p

C

L

K

3

n

(LVDS DC

Coupled)

DATA

32

DATACLK

FRAME

SYNC

PARITY

Introduction

6

SLAU374B – December 2011 – Revised May 2016

Copyright © 2011–2016, Texas Instruments Incorporated

TSW308x Evaluation Module

Figure 3. TSW30H84EVM Block Diagram