L M K 0 4 9 0 6 E V A L U A T I O N B O A R D O P E R A T I N G I N S T R U C T I O N S

SNAU126

40

For the LMK04906B, the internal VCO frequency is 2949.12 MHz. The divide-by-12 CLKout

frequency is 245.76 MHz, and the divide-by-24 CLKout frequency is 122.88 MHz.

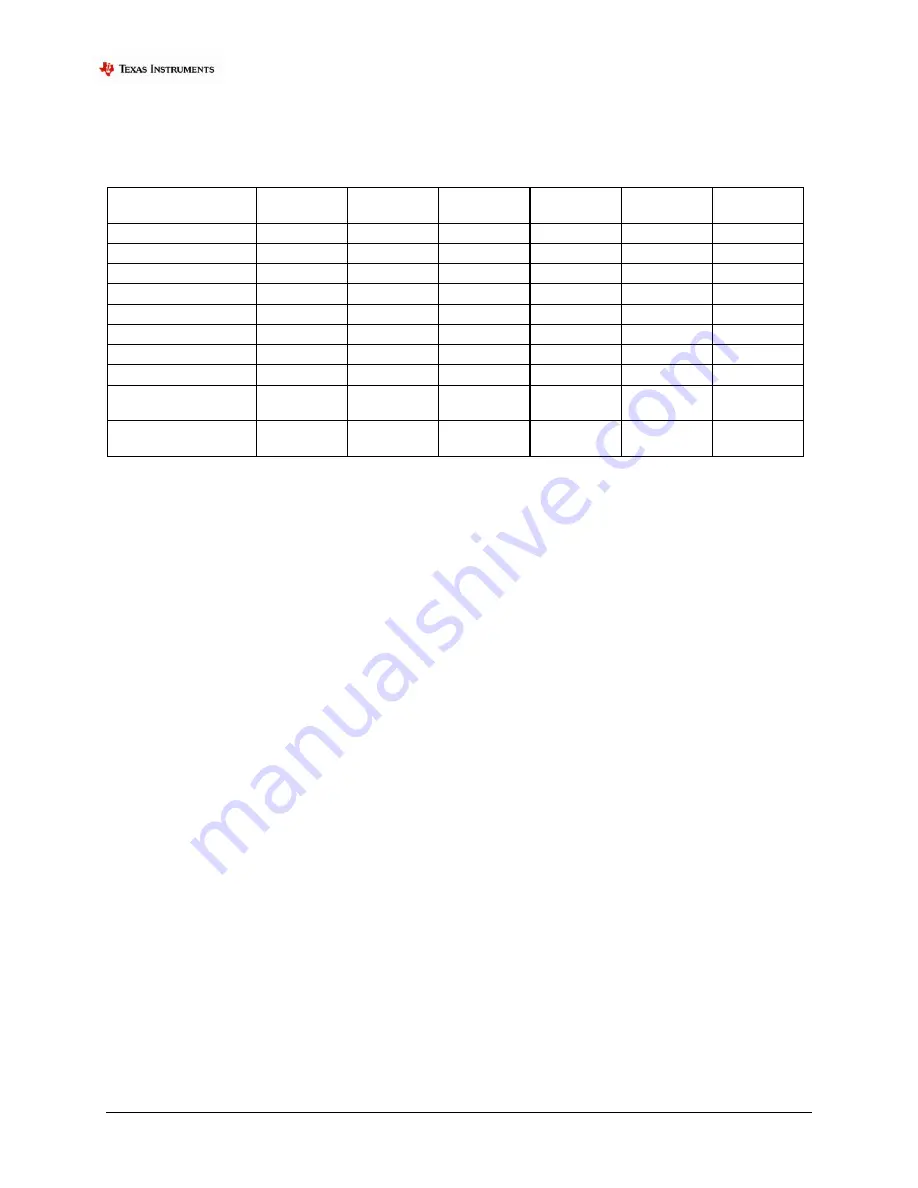

Table 15: LMK04906B Phase Noise and RMS Jitter for Different CLKout Output Formats and Frequencies

Offset

245.76

LVDS

245.76

LVPECL

245.76

LVCMOS

122.88

LVDS

122.88

LVCMOS

122.88

LVPECL

100 Hz

-106.2

-103.4

-102.9

-110.3

-110.5

-108.1

1 kHz

-124.8

-124.0

-124.1

-130.2

-130.2

-130.8

10 kHz

-133.0

-132.7

-133.7

-139.2

-137.4

-139.1

100 kHz

-135.6

-135.6

-135.7

-141.8

-141.7

-141.8

800 kHz

-147.8

-147.8

-148.3

-152.9

-153.4

-153.4

1 MHz

-149.1

-149.5

-149.2

-154.5

-155.1

-155.0

10 MHz

-156.9

-159.0

-158.0

-158.5

-161.5

-161.4

20 MHz

-157.0

-159.1

-158.1

-158.5

-161.6

-161.5

RMS Jitter (fs)

10 kHz to 20 MHz

105.1

98.1

101.7

131.1

110.7

110.6

RMS Jitter (fs)

100 Hz to 20 MHz

118.0

113.0

118.0

141.7

123.9

123.8