THCV242_ Rev.2.00_E

Copyright

©

2019 THine Electronics, Inc. THine Electronics, Inc.

44/53

Security E

6.7.

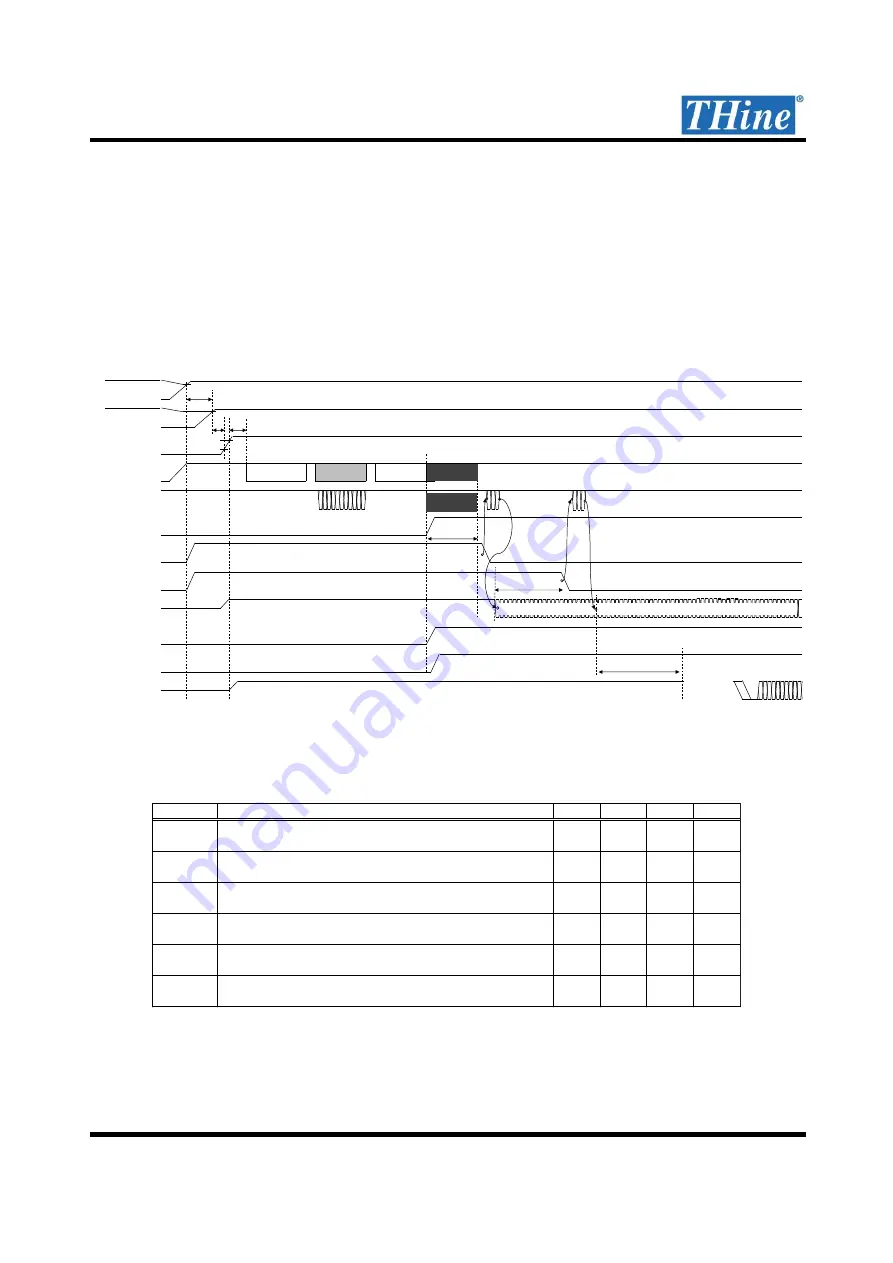

Power On Sequence

Power On Sequence must be controlled appropriate.

For Power On Reset, PDN input must be low at the moment when VDDCORE (VDD12) reach operating

condition voltage. As a note, PDN pin itself does not belongs to VDDCORE (VDD12) but to VDDIO1 (VDDH).

PDN Power On Reset control is mandatory.

MIPI, PLL and V-by-One® HS block are reset state at power on default and require Reset Release.

V-by-One® HS Soft Reset / PLL Soft Reset => MIPI Soft Reset is proper. See below detail.

Figure 14.

Power On Sequence procedure

Table 34.

Power On Sequence specification

The first MIPI output from Power On waits vertical blanking period and starts output; therefore, MIPI normal

operation may be hold for maximum 1frame, which depends on used video format.

Operating Condition min.

Operating Condition min.

t1

t2

VIH

VIL

Polling

Polling

t3

t12

Hi-Z

t6

Hi-Z

MIPI LP11

HS-mode

VDDH

(3.3V~1.8V domain)

VDD12

(1.2V domain)

PDN

THCV242

PowerON

2-wire access

prohibited

t11

2-wire remote access

THCV242

settings

Sub-Link slave

IC settings

2-wire

SCL/SDA

MIPI Tx

soft reset

MIPI Tx

TXN/P

V-by-One®HS Rx

Soft reset

V-by-One®HS

Rx HTPDN

V-by-One®HS

Rx LOCKN

V-by-One®HS

Rx RX*N/P

PLL

soft reset

Sub-Link

RCMP/N

Normal Pattern

Training Pattern

2-wire remote

access prohibited

Normal

Operation

symbol

discription

min

typ

max

unit

t1

Required w ait

from VDD33 assert to VDD12 assert

0

-

-

us

t2

Required w ait

from Pow er On to PDN High control

1000

-

-

us

t11

Required w ait

from PDN High to Register Access

300

-

-

us

t3

Time of V-by-One®HS Rx soft reset High

to HTPDN Low

-

-

10

us

t12

Time of Training Pattern Input

to LOCKN Low

-

-

980

us

t6

Time of V-by-One®HS Normal operation input

to MIPI normal operation output

-

-

50+

1frame

us