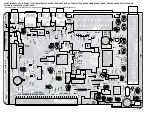

DTH8005

First issue 12 / 04

GND

PR_REC

VDDA33

VDDA33

GND

16/9_S1

I2C_DATA

I2C_CLK

+3V3SD

100N

CV042

CV043

100N

TUNER_REC

Y1_REC

GND/SCART_FB

VDEC_RST

CLA_VID[0:7]

CLA_VCLKI

VDEC_FLD

ADMCLK

+3V3SD

+1V8SD

VDEC_VS

DGND

GND

DGND

VDDX18

VDDD33

VDEC_VS

VDEC_RST

CLA_VID4

CLA_VID[0:7]

CLA_VID1

CLA_VID2

CLA_VID3

CLA_VID5

CLA_VID6

CLA_VID7

CLA_VID0

+1V8SD

CVBS1_REC

C1_REC

Y2_REC/B

DGND

DGND

DGND

DGND

DGND

DGND

DGND

CLA_VID0

DGND

DGND

DGND

DGND

+1V8SD

CV013

100N

DGND

DGND

DGND

DGND

DGND

21152800

BV001

10

9

8

7

6

5

4

3

2

1

CLA_VID5

CLA_VID2

CLA_VID3

CLA_VID4

CLA_VID6

CLA_VID7

CLA_VCLKI

DGND

CV031

100P

CLA_VCLKI

10K

RV005

C2_REC/R

Y1_REC

32M11HZ

21312930

XV001

DGND

+3V3SD

1K0

RV010

LL4448

DV001

RV012

680R0

68R0

RV007

CLA_VID1

DGND

ADMCLK

TUNER_REC

100N

CV001

+1V8SD

DGND

TPV04

+1V8SD

+3V3SD

CV014

100N

CV015

100N

CV016

100N

CV017

100N

100N

CV018

100N

CV019

CV020

100N

CV021

100N

CV022

100N

100N

CV023

CV024

100N

100N

CV026

31R0

FV002

CV032

100N

CV025

100N

VDDD18

VDDD33

GND/SCART_FB

DGND

RV013

4K7

VDDD33

CV036

100N

CV010

100N

CV037

100N

CV038

100N

CV009

100N

CV034

100N

CV039

100N

100N

CV011

CV040

100N

100N

CV005

CV012

100N

31R0

FV006

100N

CV002

CV003

100N

CV006

100N

100N

CV007

31R0

FV003

CVBS2_REC/G

TPV01

TPV02

TPV03

TPV05

CV035

100N

RV006

10K

10K

RV008

DGND

DGND

C2_REC/R

Y2_REC/B

C1_REC

CVBS2_REC/G

CVBS1_REC

VDEC_HS

I2C_CLK

I2C_DATA

CV033

100N

FV004

31R0

GND

CV045

100N

100N

CV046

GND

GND

GND

GND

CV044

100N

DGND

TPV06

VDDD33

CV004

100N

VDEC_FLD

VDEC_HS

VDDD18

DGND

RV016

0R

RV001

47R0

47R0

NV001

5

6

7

8

4

3

2

1

NV002

47R0

1

2

3

4

8

7

6

5

31R0

FV001

31R0

FV005

16/9_S2

16/9_S1

16/9_S2

CV047

47U0

PREP

RV011

100N

CV029

CV041

PREP

TV001

BC847B

4K7

RV002

RV004

47R

RV017

PREP

RV003

PREP

RV014

PREP

RV015

0R

PR_REC

RV018

0R

PB_REC

RV019

0R

Y_REC

PB_REC

Y_REC

RV020

0R

CV008

100N

EU_CVBS_REC

RV021

0R

EU_CVBS_REC

RV009

PREP

X

*

*

*

*

(M5)

VIDEO DECODER

VDDD33

(C8)

(C10)

(F12)

(H12)

(M9)

(M4)

(M8)

(M11)

(J12)

(D12)

(C9)

(C5)

DGND

VDDD18

(K4)

(J1)

(E2)

(M3)

(D4)

RV019

RV020

RV021

RV018

US

EU

X

X

X

CV030

PREP

CV027

8P2

8P2

CV028

VDDA3A

RES

HPD1

TRST

VSSA4

AI42

AI41

AGND

AI4D

AI43

VDDA4

VDDA4A

AI44

AI31

VSSA3

AI32

AI3D

AI33

VDDA3

AI34

AI21

VSSA2

AI22

AI2D

AI23

VDDA2

VDDA2A

AI24

AI11

VSSA1

AI12

AI1D

AI13

VDDA1

VDDA1A

AI14

AGNDA

AOUT1

VDDA0

VSSA0

AOUT2

VDDA_C18

VDDA_A18

DNC15

GPIN

CE

VDDD1

LLC

VSSD1

LLC2_54

VDDD2

VSSD2

TESTCLK

ADTEST9

ADTEST8

ADTEST7

ADTEST6

ADTEST5

ADTEST4

VDDD3

ADTEST3

ADTEST2

ADTEST1

VSSD3

INT_A

VDDD4

SCL

VSSD4

SDA

RTS0

RTS1

RTC0

AMCLK

VDDD5

ASCLK

ALRCLK

AMXCLK

ITRDY

OSD2

OSD1

OSD0_FSW

ICLK

IDQ

ITRI

IGP0

VSSD5

IGP1

IGPV

IGPH

IPD7

IPD5

IPD6

VDDD6

VSSD6

IPD4

IPD3

IPD2

IPD1

VDDD7

IPD0

HPD7

VSSD7

HPD6

VDDD8

HPD5

VSSD8

HPD4

HPD3

HPD2

HPD0

VDDD9

IXD7

IXD6

IXD5

IXD4

IXD3

IXD2

IXD1

IXD0

OSD3

XTRI

XPD7

XPD6

VSSD9

XPD5

XPD4

VDDD10

VSSD10

XPD3

XPD2

VDDD11

VSSD11

XPD1

XPD0

XRV

XRH

VDDD12

XCLK

XDQ

VSSD12

XRDY

TCK

TMS

TDO

VDDD13

TDI

VSSD13

VSS(XTAL)

XTALI

XTALO

VDD(XTAL)

XTOUT

DNC9

DNC10

DNC17

DNC6

SAA7119

21334090

IV001

B2

C4

C3

A2

B3

A3

B4

A4

D5

B5

C5

A5

D6

B6

C6

A6

D7

B7

A7

C8

C7

D8

A8

B8

D9

C9

A9

B9

D10

C10

A10

B10

D11

A11

C11

B11

A12

B12

A13

B13

B14

C13

C12

C14

D13

D12

D14

E11

E13

E12

E14

F11

F13

F12

F14

G11

G13

G14

H12

G12

H11

H14

H13

J11

J12

J14

J13

K11

K12

K14

K13

L11

L14

L12

L13

M14

M13

N14

N13

P13

N12

M12

P12

N11

M11

P11

L10

N10

M10

L9

P10

N9

M9

P9

L8

N8

P8

M7

M8

L7

P7

N7

L6

M6

P6

N6

L5

P5

M5

N5

L4

P4

M4

N4

P3

N3

P2

N2

N1

M2

M3

M1

L2

L3

L1

K4

K2

K3

K1

J4

J2

J3

J1

H4

H2

H1

G3

H3

G4

G1

G2

F4

F3

F1

F2

E4

E3

E1

E2

D4

D1

D3

D2

C1

C2

B1

IDR03 2ND GEN DIGITAL

VIDEO DECODER

MPEG

(DIGITAL BOARD 2/9)

MAIN SCHEMATIC DIAGRAM - SCHEMA DE LA PLATINE PRINCIPALE - SCHALTBILD HAUPTPLATINE - SCHEMA DELLA PIASTRA PRINCIPALE- ESQUEMA DE LA PLATINA PRINCIPAL